# **UCUENCA**

# Universidad de Cuenca

Facultad de Ingeniería

Carrera de Ingeniería en Telecomunicaciones

Implementación de un sistema de transmisión multiportadora sobre una plataforma FPGA

Trabajo de titulación previo a la obtencióndel título de Ingeniero en Telecomunicaciones

# **Autores:**

Henry Mauricio Castro Mendoza Jhonatan Paúl Cambisaca Sánchez

## **Director:**

Kenneth Samuel Palacio Baus

ORCID: 0000-0002-7318-8062

## Co-Director:

Lizandro Damián Solano Quinde

ORCID: 0000-0001-7427-4889

Cuenca, Ecuador

2024-09-13

#### Resumen

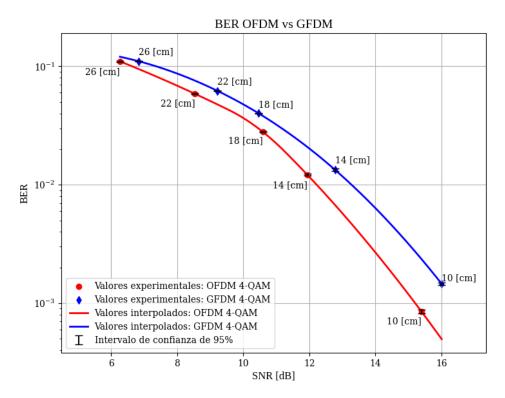

Los sistemas de modulación multiportadora aumentan la tasa de bits en comunicaciones digitales y optimizan el uso del ancho de banda, en comparación con los sistemas de modulación de portadora única. En este trabajo, se implementan los sistemas OFDM y GFDM en una FPGA STEMLab 125-14 de Red Pitaya. La implementación de un sistema de transmisión multiportadora en una FPGA implica trasladar conceptos matemáticos complejos a nivel de hardware. Por tanto, es esencial dominar el entorno de descripción de hardware para abordar problemas de síntesis y retardos. Esto para formar un sistema de transmisión autónomo, sin necesidad de hardware externo. La implementación de OFDM y GFDM se basa en la representación vectorial de los sistemas multiportadora, cuyas características dependen del filtro formador de pulsos. En OFDM se emplea un pulso rectangular, mientras que en GFDM se usa un filtro de coseno elevado. Ambos sistemas utilizan símbolos 4-QAM y tramas de sincronización para facilitar la recepción. Para evaluar el sistema, se utiliza el dispositivo HackRF One junto con el software GNU Radio. La señal recibida se compara con la teórica mediante una correlación cruzada y se mide la tasa de error de bits (BER) en función de la distancia. Los resultados demuestran que la señal recibida coincide con la simulada y se observa que GFDM requiere un 7% más de SNR que OFDM para lograr una tasa de error similar. Estos resultados confirman la correcta implementación y establecen las bases para el desarrollo de nuevas tecnologías en sistemas de comunicación multiportadora.

Palabras clave del autor: programación paralela, sistema de transmisión, sistemas multiportadoras

El contenido de esta obra corresponde al derecho de expresión de los autores y no compromete el pensamiento institucional de la Universidad de Cuenca ni desata su responsabilidad frente a terceros. Los autores asumen la responsabilidad por la propiedad intelectual y los derechos de autor.

Repositorio Institucional: https://dspace.ucuenca.edu.ec/

## **Abstract**

Multicarrier modulation systems increase the bit rate in digital communications and optimize bandwidth usage compared to single carrier modulation systems. In this work, we implement OFDM and GFDM systems on a Red Pitaya FPGA STEMLab 125-14 platform. Implementing a multicarrier transmission system on an FPGA involves translating complex mathematical concepts into hardware-level operations. Mastery of the hardware description environment is crucial for addressing synthesis and delay issues, enabling the creation of a standalone transmission system without external hardware. The implementation of OFDM and GFDM is based on the vector representation of multicarrier systems, where the characteristics depend on the pulse-shaping filter used. OFDM employs a rectangular pulse, while GFDM uses a raised cosine filter. Both systems utilize 4-QAM symbols and synchronization frames to facilitate signal reception. To evaluate the system, we use the HackRF One device in conjunction with GNU Radio software. The received signal is compared with the theoretical signal using crosscorrelation, and the bit error rate (BER) is measured as a function of distance. The results show that the received signal closely matches the simulated signal and it was observed that GFDM requires 7% more SNR than OFDM to achieve a similar error rate. These findings validate the implementation and lay the groundwork for developing new technologies in multicarrier communication systems.

Author keywords: parallel programming, transmission system, multicarrier systems

The content of this work corresponds to the right of expression of the authors and does not compromise the institutional thinking of the University of Cuenca, nor does it release its responsibility before third parties. The authors assume responsibility for the intellectual property and copyrights.

Institutional Repository: https://dspace.ucuenca.edu.ec/

# Índice de contenido

| 1. | Gen  | eralidades                                                          | 14 |  |  |  |  |  |

|----|------|---------------------------------------------------------------------|----|--|--|--|--|--|

|    | 1.1. | Introducción                                                        | 14 |  |  |  |  |  |

|    | 1.2. | Objetivos                                                           | 15 |  |  |  |  |  |

|    |      | 1.2.1. Objetivo general                                             | 15 |  |  |  |  |  |

|    |      | 1.2.2. Objetivos específicos                                        | 15 |  |  |  |  |  |

|    | 1.3. | Alcance                                                             | 15 |  |  |  |  |  |

|    | 1.4. | Justificación                                                       | 16 |  |  |  |  |  |

| 2. | Marc | co Teórico                                                          | 18 |  |  |  |  |  |

|    | 2.1. | Sistemas de Modulación Multiportadora                               | 18 |  |  |  |  |  |

|    |      | 2.1.1. Orthogonal Frequency Division Multiplexing: OFDM             | 18 |  |  |  |  |  |

|    |      | 2.1.1.1. Beneficios de la modulación OFDM en comunicaciones inalám- |    |  |  |  |  |  |

|    |      | bricas                                                              | 18 |  |  |  |  |  |

|    |      | 2.1.1.2. Modelo en Bloques del Sistema de Transmisión OFDM          | 19 |  |  |  |  |  |

|    |      | 2.1.1.3. Problemas Asociados con OFDM                               | 21 |  |  |  |  |  |

|    |      | 2.1.2. Técnicas avanzadas de acceso múltiple para 5G                | 22 |  |  |  |  |  |

|    |      | 2.1.2.1. Generalized Frequency Division Multiplexing: GFDM          | 22 |  |  |  |  |  |

|    | 2.2. | Sistemas de Radio definidos por Software: SDR                       | 26 |  |  |  |  |  |

|    |      | 2.2.1. HackRF One                                                   | 27 |  |  |  |  |  |

|    |      | 2.2.2. GNU Radio                                                    | 29 |  |  |  |  |  |

|    | 2.3. | Field Programmable Gate Array                                       |    |  |  |  |  |  |

|    |      | 2.3.1. Características técnicas de los dispositivos FPGA            | 30 |  |  |  |  |  |

|    |      | 2.3.2. Spartan 3E                                                   | 30 |  |  |  |  |  |

|    |      | 2.3.3. Basys 3                                                      | 31 |  |  |  |  |  |

|    |      | 2.3.4. STEMlab 125-14                                               | 32 |  |  |  |  |  |

|    | 2.4. | Método Analytic Hierarchy Process                                   | 33 |  |  |  |  |  |

|    |      | 2.4.1. Metodología del Análisis Jerárquico AHP                      | 33 |  |  |  |  |  |

|    |      | 2.4.2. Estructuración de los niveles de jerarquía                   | 34 |  |  |  |  |  |

|    |      | 2.4.3. Escala fundamental de Saaty                                  | 34 |  |  |  |  |  |

|    |      | 2.4.4. Matrices de comparación y cálculo de prioridades             | 36 |  |  |  |  |  |

|    |      | 2.4.5. Consistencia del Análisis                                    | 36 |  |  |  |  |  |

|    |      | 2.4.6. Síntesis de Prioridades                                      | 38 |  |  |  |  |  |

|    | 2.5. | Trabajos Relacionados                                               | 38 |  |  |  |  |  |

| 3. | Des  | arrollo | del Sistema                                                                | 41 |

|----|------|---------|----------------------------------------------------------------------------|----|

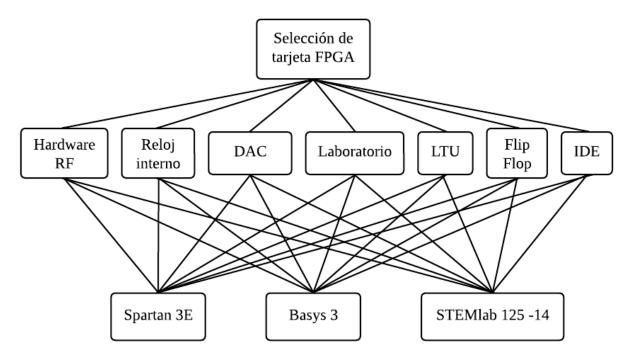

|    | 3.1. | Anális  | is de los dispositivos FPGA disponibles en la Universidad de Cuenca        | 41 |

|    |      | 3.1.1.  | Definición el Problema                                                     | 41 |

|    |      | 3.1.2.  | Diseño de la estructura jerárquica con AHP para la selección de la tarjeta |    |

|    |      |         | FPGA                                                                       | 41 |

|    |      | 3.1.3.  | Criterios de evaluación para el análisis del Proceso de Jerarquía Analíti- |    |

|    |      |         | ca (AHP)                                                                   | 42 |

|    |      | 3.1.4.  | Comparación de los criterios                                               | 43 |

|    |      | 3.1.5.  | Comparación por pares para cada criterio                                   | 46 |

|    |      |         | 3.1.5.1. Hardware RF                                                       | 46 |

|    |      |         | 3.1.5.2. Reloj Interno                                                     | 46 |

|    |      |         | 3.1.5.3. Conversor digital analógico (DAC)                                 | 47 |

|    |      |         | 3.1.5.4. Laboratorio                                                       | 47 |

|    |      |         | 3.1.5.5. Look-Up Tables (LUT)                                              | 47 |

|    |      |         | 3.1.5.6. Flip Flop                                                         | 48 |

|    |      |         | 3.1.5.7. Entornos de desarrollo (IDE)                                      | 48 |

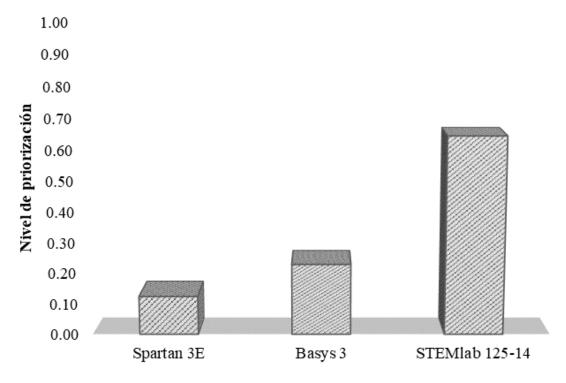

|    |      | 3.1.6.  | Matriz de prioridades de criterios y opciones                              | 48 |

|    |      | 3.1.7.  | Interpretación de los Resultados                                           | 49 |

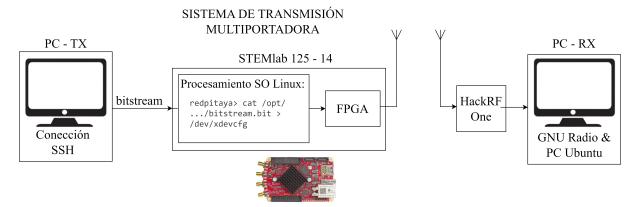

|    | 3.2. | Esque   | ma del sistema de comunicación                                             | 50 |

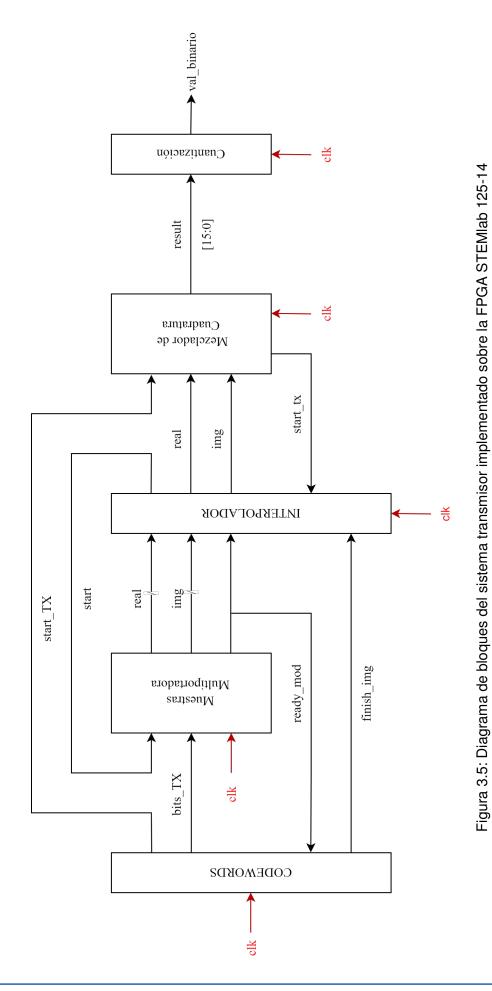

|    | 3.3. | Impler  | mentación del Sistema de Transmisión sobre la FPGA                         | 51 |

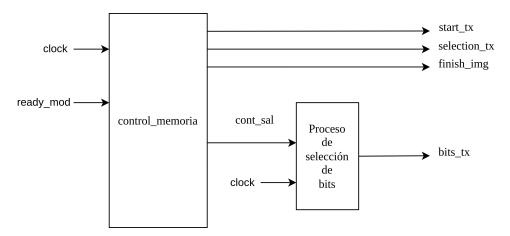

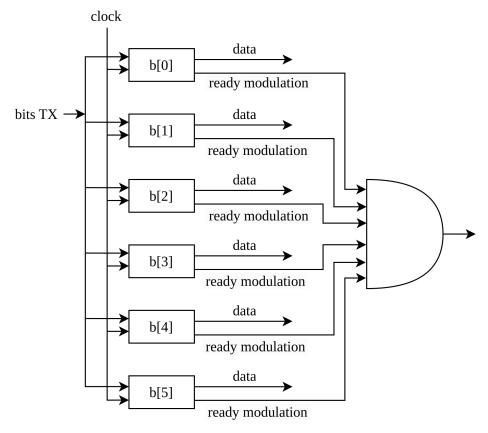

|    |      | 3.3.1.  | Codewords                                                                  | 54 |

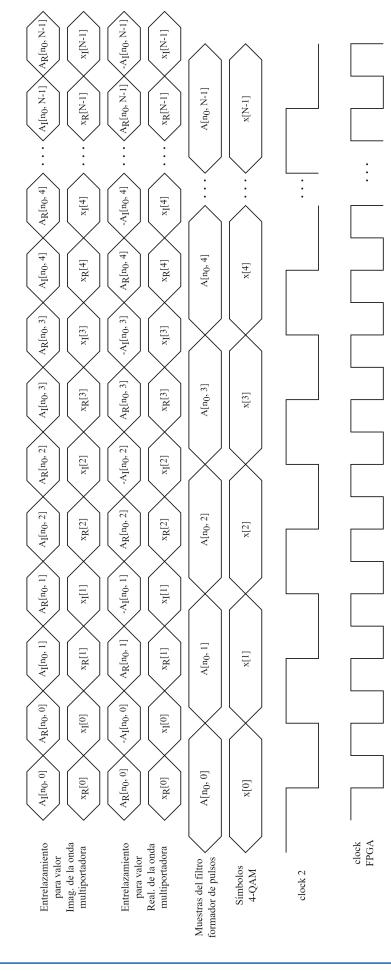

|    |      | 3.3.2.  | Generación de muestras multiportadora (OFDM/GFDM)                          | 56 |

|    |      |         | 3.3.2.1. Modelo Matemático de Sistemas Multiportadoras                     | 56 |

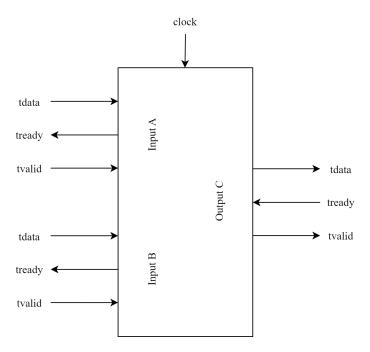

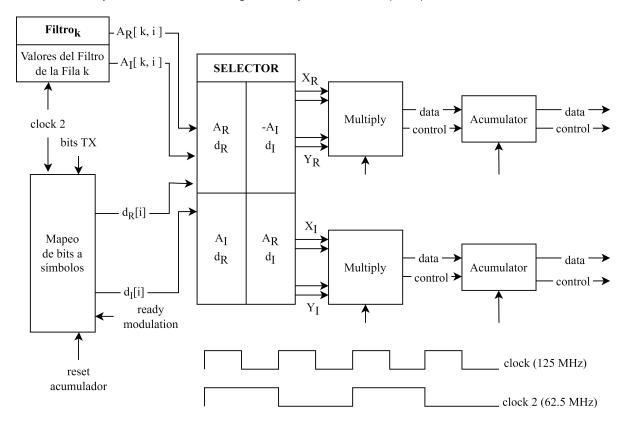

|    |      |         | 3.3.2.2. Diseño del producto matriz-vector en VHDL                         | 57 |

|    |      |         | 3.3.2.3. Implementación de OFDM en VHDL                                    | 62 |

|    |      |         | 3.3.2.4. Implementación de GFDM en VHDL                                    | 64 |

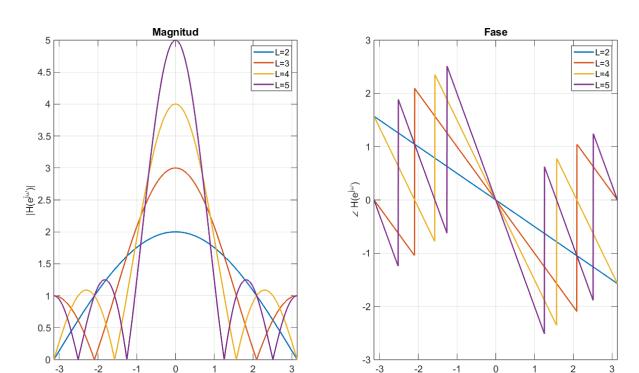

|    |      | 3.3.3.  | Interpolador                                                               | 65 |

|    |      |         | 3.3.3.1. Descripción Matemática                                            | 65 |

|    |      |         | 3.3.3.2. Diseño en VHDL                                                    | 66 |

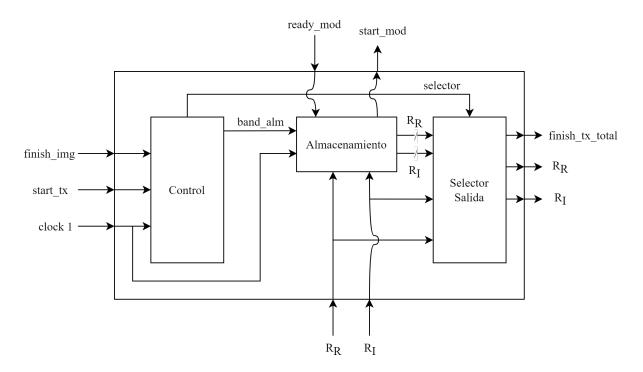

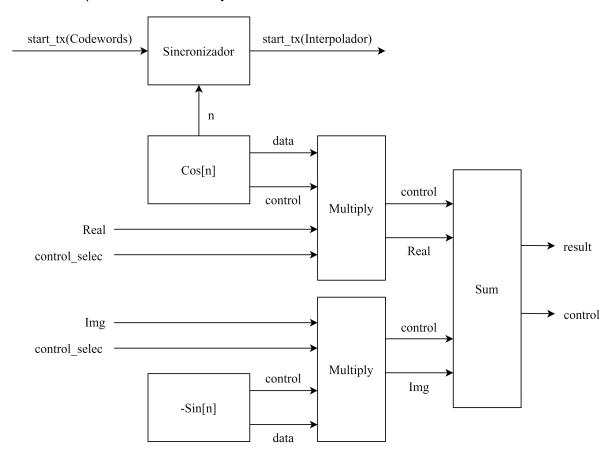

|    |      | 3.3.4.  | Mezclador de Cuadratura                                                    | 70 |

|    |      | 3.3.5.  | Cuantización uniforme                                                      | 72 |

|    |      |         | 3.3.5.1. Descripción Matemática                                            | 72 |

|    |      |         | 3.3.5.2. Diseño en VHDL                                                    | 73 |

|    | 3.4. | Desar   | rollo de Receptor                                                          | 76 |

| Re | 5.4.<br>ferer | ,       | os Futuro  |                                                                 | 102<br>103 |

|----|---------------|---------|------------|-----------------------------------------------------------------|------------|

|    | 5.4.          | Trabaj  | os Futuro  | 5                                                               | 102        |

|    |               |         |            | S                                                               |            |

|    | 5.3.          | Recon   | nendacior  | nes                                                             | 101        |

|    | 5.2.          | Desafí  | os en la l | Implementación                                                  | 100        |

|    | 5.1.          | Conclu  | usiones .  |                                                                 | 99         |

| 5. | Con           | clusior | nes, Desa  | afíos, Recomendaciones y Trabajos Futuros                       | 99         |

|    |               | 4.2.2.  | Evaluaci   | ión del experimento 2                                           | 96         |

|    |               | 4.2.1.  | Evaluaci   | ión del experimento 1                                           | 92         |

|    | 4.2.          | Result  | ados de l  | a evaluación experimental                                       | 92         |

|    |               | 4.1.2.  | Metodolo   | ogía para realizar el experimento 2                             | 92         |

|    |               | 4.1.1.  | Metodolo   | ogía para realizar el experimento 1                             | 91         |

|    | 4.1.          | Metod   | ología pa  | ra realizar las pruebas y mediciones                            | 90         |

| 4. | Eval          | uación  | del Sist   | ema                                                             | 90         |

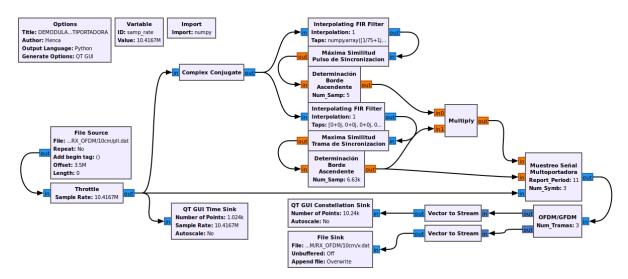

|    |               |         | 3.4.3.2.   | Demodulador Multiportadora                                      | 87         |

|    |               |         |            | Receptor RF                                                     |            |

|    |               | 3.4.3.  | ·          | entación del sistema de recepción multiportadora en GNU Radio . |            |

|    |               |         | 3.4.2.8.   | Bloques de procesamiento de resultados                          | 85         |

|    |               |         | 3.4.2.7.   | Bloques de visualización de resultados                          | 85         |

|    |               |         | 3.4.2.6.   | Bloques de conversión                                           | 85         |

|    |               |         |            | Python                                                          | 85         |

|    |               |         | 3.4.2.5.   | Bloque Embedded Python Block para la adición de código en       |            |

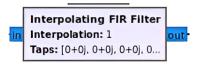

|    |               |         | 3.4.2.4.   | Bloque de filtrado Interpolating FIR Filter                     | 84         |

|    |               |         | 3.4.2.3.   | Bloque PLL Carrier Tracking corrector de fase                   | 83         |

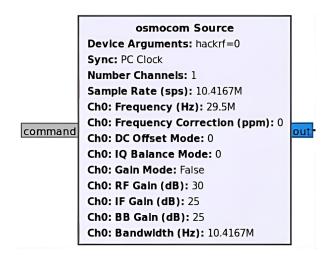

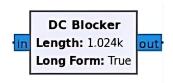

|    |               |         | 3.4.2.2.   | Bloque DC Blocker                                               | 82         |

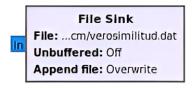

|    |               |         | 3.4.2.1.   | Bloque Osmocom source para la recepción de la señal             | 81         |

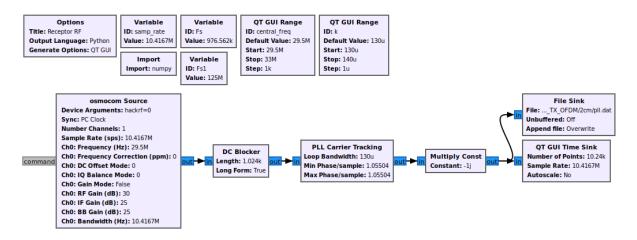

|    |               | 3.4.2.  | Software   | e GNU Radio                                                     | 81         |

|    |               |         | 3.4.1.3.   | Demodulador Multiportadora                                      | 80         |

|    |               |         |            | Detección de inicio de tramas multiportadora                    |            |

|    |               |         | 3.4.1.1.   | Desfases entre los relojes del sistema transmisor y receptor    | 77         |

|    |               | 3.4.1.  | Analisis   | matemático para la implementación del receptor en GNU Radio.    | //         |

# Índice de figuras

| 2.1.  | Principio fundamental de la modulación OFDM. Fuente: [1]                       | 20 |

|-------|--------------------------------------------------------------------------------|----|

| 2.2.  | Diagrama de bloques de un sistema transmisor típico para una modulación        |    |

|       | OFDM. Fuente: [2]                                                              | 21 |

| 2.3.  | Acceso múltiple para la tecnología del futuro. Fuente: [3] © 2016 IEEE         | 23 |

| 2.4.  | Partición del tiempo y la frecuencia GFDM. Fuente: [4] © 2014 IEEE             | 23 |

| 2.5.  | Sistemas de comunicaciones GFDM. Fuente: [4] © 2014 IEEE                       | 24 |

| 2.6.  | Modulador GFDM. Fuente: [4] © 2014 IEEE                                        | 24 |

| 2.7.  | Diagrama de bloques del receptor SDR. Fuente: [5]                              | 27 |

| 2.8.  | Dispositivo HackRF One. Fuente: [6].                                           | 28 |

| 2.9.  | Diagrama de bloques del lado receptor del HackRF One. Fuente: [7]              | 28 |

| 2.10. | .Bloque Osmocom de GNU-RADIO. Fuente: [8]                                      | 29 |

| 2.11. | .Dispositivo FPGA Spartan 3E. Fuente: [9]                                      | 31 |

| 2.12. | .Dispositivo FPGA Basys 3. Fuente: [10]                                        | 32 |

| 2.13. | .Dispositivo FPGA STEMlab 125-14. Fuente: [11]                                 | 32 |

| 2.14. | .Estructura jerárquica del método AHP. Fuente: [12]                            | 35 |

| 2 1   | Esquema Jerárquico para la selección de la tarjeta FPGA                        | 12 |

|       | Resultado del análisis AHP.                                                    |    |

|       | Visión global del sistema de comunicaciones implementado                       |    |

|       | IP Core Floating Point                                                         |    |

|       | Diagrama de bloques del sistema transmisor implementado sobre la FPGA STEM-    | 52 |

| 3.5.  |                                                                                | 53 |

| 2.6   |                                                                                |    |

|       | Comportamiento de la interacción entre los valores flotantes pertenecientes a  | 55 |

| 3.7.  | ·                                                                              | 50 |

| 2.0   | las muestras del filtro formador de pulsos y los símbolos 4-QAM                |    |

|       | Diagrama de bloques para la obtención de una muestra de la onda multiportadora | 60 |

| ა.ყ.  | Diagrama de bloques simplificado de la implementación del producto matriz-     | 61 |

| 2 10  | Vector                                                                         |    |

|       | Respuesta al Impulso del filtro pasa bajo en el dominio de la frecuencia       |    |

|       | Diagrama de Bloques del componente Interpolador                                |    |

|       | Diagrama de Bloques del componente Mezclador de Cuadratura                     |    |

| 3.13. | .Diagrama de Bloques del componente cuantizador.                               | 15 |

| 3.14 | . Diagrama esquematico del bioque Generador de Senales del ejemplo Frequency |     |

|------|------------------------------------------------------------------------------|-----|

|      | Counter. Fuente: [13]                                                        | 75  |

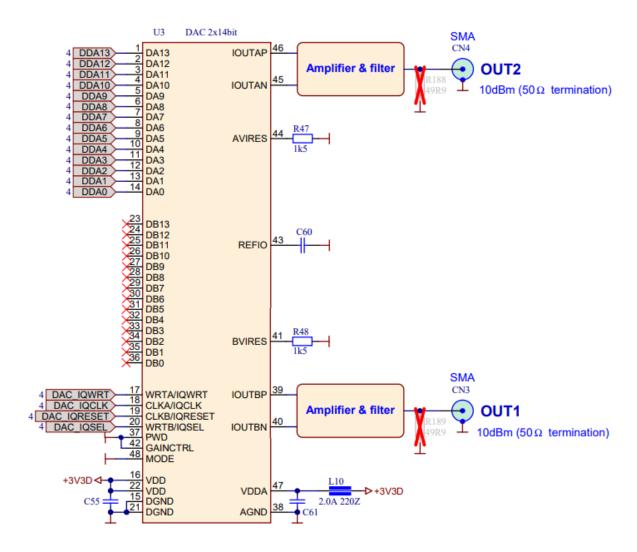

| 3.15 | .Circuitería RF en STEMlab 125-14. Fuente: [14]                              | 76  |

| 3.16 | .Configuración para el bloque Osmocom. Fuente: [8]                           | 82  |

| 3.17 | .Configuración para el bloque DC Blocker. Fuente: [15]                       | 82  |

| 3.18 | .Configuración para el bloque PLL Carrier Tracking. Fuente: [16]             | 84  |

| 3.19 | .Configuración para el bloque Interpolating FIR Filter. Fuente: [15]         | 84  |

| 3.20 | .Configuración para el bloque File Sink. Fuente: [17]                        | 85  |

| 3.21 | .Configuración para el bloque File Source. Fuente: [18]                      | 86  |

| 3.22 | .Receptor RF implementado en GNU Radio                                       | 87  |

| 3.23 | .Demodulador Multiportadora implementado en GNU Radio                        | 89  |

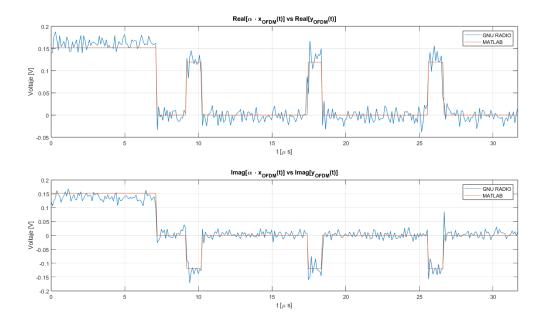

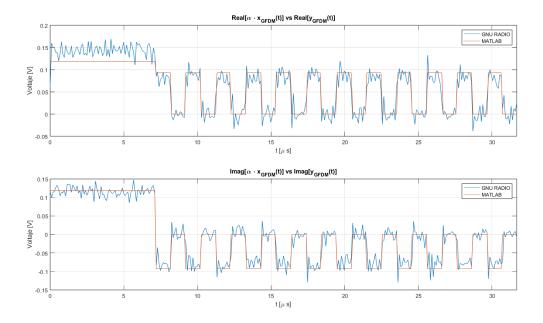

| 4.1. | Señal OFDM receptada versus señal OFDM simulada                              | 94  |

| 4.2. | Señal GFDM receptada versus señal GFDM simulada                              | 95  |

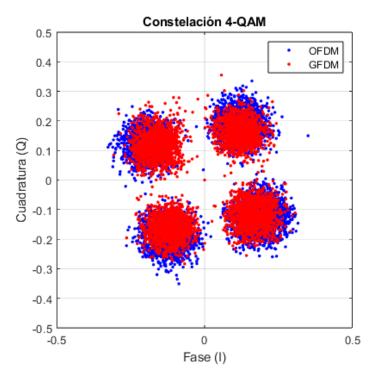

| 4.3. | Constelaciones 4-QAM para OFDM y GFDM                                        | 95  |

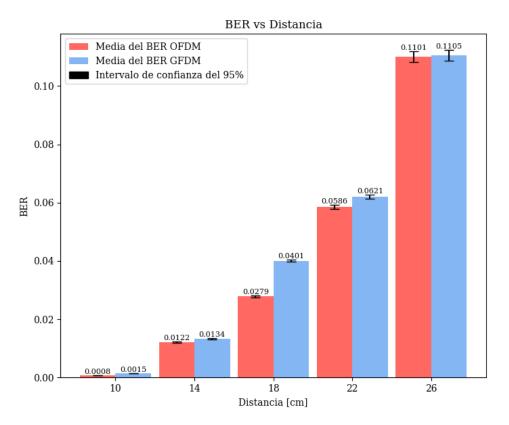

| 4.4. | Comparación del BER vs Distancia para modulaciones OFDM y GFDM               | 97  |

| 4.5. | Comparación del BER vs SNR para modulaciones OFDM y GFDM                     | 98  |

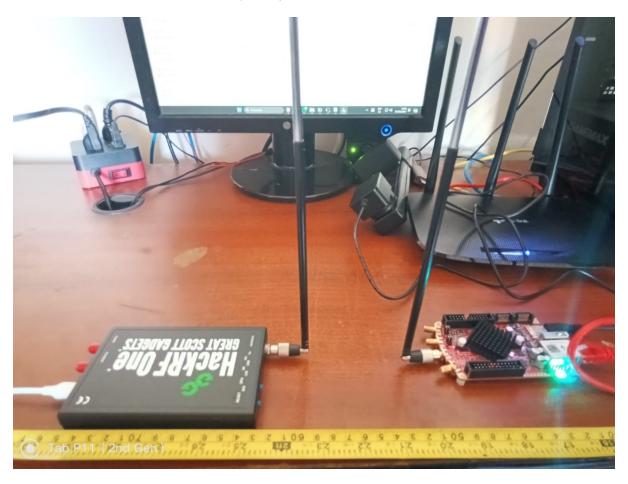

| A1.  | Ejecución de los experimentos 1 y 2                                          | 111 |

# Índice de tablas

| 2.1. | Características técnicas de los dispositivos FPGA. Fuentes: [9] [19] [20] [10] [11] |    |

|------|-------------------------------------------------------------------------------------|----|

|      | [21]                                                                                | 30 |

| 2.2. | Escala fundamental de Saaty. Fuente: [22]                                           | 35 |

| 2.3. | Ejemplo de Matriz de Comparación Pareada                                            | 36 |

| 2.4. | Tabla de referencia para el índice de consistencia aleatorio. Fuente: [23]          | 38 |

| 3.1. | Matriz de comparación de criterios                                                  | 44 |

| 3.2. | Matriz de comparación de criterios normalizada                                      | 44 |

| 3.3. | Matriz de comparación para el criterio: Hardware RF                                 | 46 |

| 3.4. | Matriz de comparación para el criterio: Reloj Interno                               | 46 |

| 3.5. | Matriz de comparación para el criterio: DAC                                         | 47 |

| 3.6. | Matriz de comparación para el criterio: Laboratorio                                 | 47 |

| 3.7. | Matriz de comparación para el criterio: LUTs                                        | 47 |

| 3.8. | Matriz de comparación para el criterio: Flip Flop                                   | 48 |

| 3.9. | Matriz de comparación para el criterio: IDE                                         | 48 |

| 3.10 | .Matriz de resultados del análisis AHP.                                             | 49 |

| 3.11 | .Parámetros de señales multiportadoras                                              | 70 |

| 3.12 | Descripción de los bloques y señales en el proceso de cuantización uniforme         | 74 |

| 3.13 | Parámetros de configuración del bloque Osmocom Source de GNU Radio                  | 83 |

| 4.1. | Resultados del experimento 2                                                        | 96 |

# **Dedicatoria**

A mis padres Zoila y Carlos por todo su apoyo incalculable de aportes a mi vida y por ser el pilar fundamental en mi formación personal y profesional. A mis hermanos con quienes he compartido toda mi vida les agradezco inmensurablemente todo su sacrificio y cariño entregado, a todos ustedes dedico este trabajo de integración curricular. Gracias por todo.

**Jhonatan**

# **Dedicatoria**

Dedico este trabajo de integración curricular a mis padres Henry y Diana, quienes me brindaron su apoyo incondicional durante toda mi formación académica y representaron mi primera escuela en la instrucción de valores, ayudándome a convertirme en una persona de bien.

Mauricio

# **Agradecimientos**

Agradecemos a nuestros tutores, Ing. Kenneth Palacio e Ing. Lizandro Solano, por su apoyo académico y emocional durante el desarrollo de este trabajo. Su experiencia y compromiso han sido esenciales para su culminación.

También agradecemos a los ingenieros Ing. Fabian Astudillo e Ing. Alcides Araujo por facilitar el acceso a los equipos FPGA necesarios a través de la Universidad de Cuenca.

Finalmente, extendemos nuestro agradecimiento a todos los ingenieros que han contribuido a nuestra formación académica, cuyo conocimiento se refleja en este trabajo de integración curricular.

**Henry Mauricio Castro Mendoza**

Jhonatan Paúl Cambisaca Sánchez

## Generalidades

# 1.1. Introducción

Los sistemas de comunicación móvil se han convertido en una herramienta universal indispensable, lo que ha impulsado su evolución continua desde su creación. Durante el apogeo de la tecnología 3G, se identificó la necesidad de incrementar tanto la velocidad como la capacidad de los sistemas de comunicación existentes. En marzo de 2003, la 3rd Generation Partnership Project (3GPP) realizó un Estudio de Viabilidad de OFDM (Orthogonal Frequency Division Multiplexing) para la mejora de UTRAN (Universal Terrestrial Radio Access Network) [24]. Según la 3GPP, OFDM es la técnica adecuada para la multiplexación y el acceso al medio, especialmente para los servicios multimedia que requieren alta velocidad y robustez en la transmisión.

En diciembre de 2005, OFDM fue reconocida como la técnica idónea para el acceso al medio, y su primera estandarización fue aprobada en 2007 [1]. Actualmente, las redes móviles 4G están ampliamente desplegadas a nivel mundial. Sin embargo, la tecnología de redes móviles vigente enfrenta limitaciones en cuanto a la velocidad de transmisión y las técnicas de multiacceso, lo que ha generado la necesidad de utilizar modulaciones de orden superior para transmitir mayor cantidad de información dentro del mismo ancho de banda.

Una de las técnicas propuestas como candidata para su uso en las redes móviles 5G es la tecnología *Generalized Frequency Division Multiplexing* (GFDM), caracterizada por utilizar filtros formadores de pulso con formas de onda más flexibles y no necesariamente ortogonales, a diferencia de OFDM. Aunque GFDM es considerada una alternativa viable para 5G, la literatura revela un vacío en el desarrollo de sistemas transmisores multiportadora en plataformas FPGA (*Field-Programmable Gate Array*), particularmente en lo que respecta a la implementación de un modulador GFDM en este tipo de hardware, el mismo que por su versatilidad facilita el desarrollo de prototipos y sistemas comerciales.

El presente trabajo tiene como objetivo diseñar e implementar un sistema de transmisión multiportadora sobre una plataforma FPGA, enfocándose en resolver la complejidad de configurar un sistema de multiplexación por división de frecuencia en una plataforma de descripción de hardware como VHDL (*VHSIC Hardware Description Language*). La evaluación del sistema se realizará a través de un SDR (*Software-Defined Radio*) que utiliza GNU Radio para el proceso de demodulación. Este proyecto busca comparar los sistemas de modulación OFDM y GFDM a nivel de prueba de concepto teórico-práctico con fines educativos y de investigación.

# 1.2. Objetivos

# 1.2.1. Objetivo general

Implementar un sistema de transmisión basado en esquemas de modulación multiportadora sobre una plataforma embebida FPGA.

# 1.2.2. Objetivos específicos

- 1. Analizar distintas plataformas FPGA disponibles en la Universidad de Cuenca y su viabilidad para el desarrollo de sistemas de comunicaciones multiportadora.

- 2. Implementar un sistema transmisor con modulación multiportadora sobre una plataforma embebida FPGA.

- 3. Evaluar el rendimiento del transmisor mediante un receptor implementado en *Software Defined Radio*.

# 1.3. Alcance

El trabajo de integración curricular se enfoca en la implementación de dos sistemas de transmisión multiportadora. El primer sistema corresponde a la modulación OFDM, descrita mediante un algoritmo de Transformada Discreta de Fourier Inversa (I-DFT) en lugar del uso convencional de la Transformada Rápida de Fourier Inversa (I-FFT) para el proceso de modulación. El segundo sistema emplea la modulación *Generalized Frequency Division Multiplexing* (GFDM), considerada una opción prometedora para la tecnología 5G. Entre otras, una de las metas de este trabajo es realizar una evaluación comparativa entre ambas modulaciones.

Ambos sistemas de modulación están precedidos por una premodulación QAM de 4 símbolos, utilizando la codificación Gray en el mapeo de símbolos. Fuera de esta codificación, el sistema de transmisión no incorpora técnicas de entrelazado ni mecanismos de detección y corrección de errores.

En la modulación OFDM, se emplea la I-DFT de seis símbolos, acompañada de un prefijo cíclico de 2 muestras. Por otra parte, en la modulación GFDM se utilizan tanto subsímbolos como subportadoras, con la capacidad de transmitir 6 símbolos pertenecientes a 4-QAM, durante una trama GFDM.

La metodología del trabajo de integración curricular consta de los siguientes pasos:

- Investigar y desarrollar las expresiones matemáticas que modelan el comportamiento de los sistemas de modulación multiportadora.

- Comprender el estándar IEEE 754 para gestionar la representación de números en punto flotante en Vivado (la suite de desarrollo para FPGA de Xilinx¹).

- Seleccionar una tarjeta FPGA que cumpla con los requisitos necesarios para el desarrollo del proyecto de titulación.

- Realizar la descripción del hardware utilizando VHDL para implementar una modulación multiportadora en una FPGA.

- Verificar el proceso de descripción del hardware del transmisor mediante depuración

(Debug) para confirmar la síntesis del proyecto en el entorno de Vivado.

- Realizar pruebas y validar el sistema de transmisión multiportadora utilizando GNU Radio, demodulando la señal.

Como resultado del trabajo de integración curricular, se espera obtener un sistema de transmisión multiportadora funcional que pueda ser utilizado por la Universidad de Cuenca para fomentar el aprendizaje en la carrera de telecomunicaciones, específicamente en el área de laboratorio. Además, este proyecto establece un precedente en la implementación de la modulación GFDM sobre una plataforma de hardware FPGA.

# 1.4. Justificación

Los sistemas de comunicación multiportadora se exploran y evalúan comúnmente en la carrera de Telecomunicaciones mediante simulaciones en software, como MatLab [25] entre otros. Sin embargo, los lenguajes de alto nivel usados en estos simuladores, no permiten de manera general, una implementación eficiente y que pueda funcionar en tiempo real, además de consumir recursos de cómputo considerables. En este sentido, la implementación de una modulación multiportadora en una plataforma FPGA abre las oportunidades de implementar un procesamiento más eficiente, y en el que se pueda explorar diferentes arquitecturas. El uso de hardware reconfigurable además facilita el prototipado, la evaluación de consumo energético y limitaciones de procesamiento.

https://www.xilinx.com/products/design-tools/vivado.html

En contraste, la implementación de un algoritmo enteramente a través de software en un lenguaje de alto nivel es una herramienta valiosa para la visualización de un esquema de modulación. Se puede mencionar la facilidad de uso de herramientas como MatLab, en donde el lenguaje facilita muchos procedimientos mediante funciones que deslindan al usuario cualquier necesidad de conocer la arquitectura sobre la cual se ejecuta el código (que para Matlab corre sobre una máquina virtual de Java). No obstante, la implementación de una modulación multiportadora utilizando un lenguaje de bajo nivel como VHDL, posibilita reducir el uso de recursos en comparación a aquel que demanda una aplicación por software sobre un computador. Una implementación en hardware adicionalmente ofrece múltiples oportunidades de aprendizaje, y crea precedentes para futuros proyectos en la misma línea de trabajo. Realizar la implementación de un sistema de transmisión multiportadora sobre una plataforma embebida FPGA permitirá comprender mejor los desafíos que presentan estos esquemas de modulación desde el punto de vista de la práctica de ingeniería y su convergencia con la teoría. La experiencia adquirida en la implementación física proporcionará una base sólida para el diseño de sistemas de comunicaciones multiportadora más complejos

Con propósitos de validación y verificación de la implementación del transmisor realizado en la plataforma FPGA, se utilizará un receptor basado en *Software Defined Radio* (SDR) [15]. El uso de SDR se ha masificado en años recientes, gracias a la flexibilidad que se maneja en este tipo de sistemas. SDR se utilizan hoy en día ampliamente en la investigación, la industria y la academia. En este contexto, se propone el uso de GNU Radio, en conjunción con herramientas de hardware RF externo comercial para la recepción de señales. La programación de código abierto (*Open Source*) que emplea GNU radio permite configurar los parámetros del demodulador para conseguir la información transmitida. Al mismo tiempo, el uso de GNU radio facilitará la creación e implementación de modelos de evaluación del sistema mediante la medición del BER, entre otros, utilizando herramientas de terceros para la generación de datos, por ejemplo, MatLab.

# Marco Teórico

# 2.1. Sistemas de Modulación Multiportadora

Un sistema de modulación multiportadora divide su ancho de banda en varios segmentos pequeños, cada uno de los cuales es transmitido usando una subportadora distinta. Esto significa que la información se envía a través de varias subportadoras dentro del ancho de banda en lugar de usar una sola frecuencia portadora. Esta característica hace que los sistemas multiportadora sean resistentes al desvanecimiento rápido de los canales inalámbricos. Por esta razón, las modulaciones multiportadora se utilizan en las comunicaciones móviles, ya que su robustez ayuda a mitigar los efectos de la movilidad, la sección 3.3.2.1 proporciona una descripción más detallada.

# 2.1.1. Orthogonal Frequency Division Multiplexing: OFDM

La Multiplexación por División de Frecuencias Ortogonales (OFDM) es una técnica de modulación multiportadora que divide el espectro disponible en subportadoras ortogonales de banda

estrecha para transmitir datos simultáneamente, lo que la hace resistente a interferencias y

efectos multitrayecto [26] [27] [28]. Un aspecto interesante de OFDM, es que utiliza la Transformada Rápida de Fourier (FFT) y la Transformada Rápida de Fourier Inversa (IFFT) para generar subportadoras ortogonales para la transmisión paralela de señales digitales, asegurando

una alta eficiencia espectral y propiedades anti dispersión [29]. Este esquema de modulación

ha encontrado aplicaciones en diversos campos como enlaces de datos *Synthetic Aperture Radar* (SAR), redes inalámbricas 5G, canales acústicos submarinos y sistemas de comunicación por fibra óptica, donde ha mejorado significativamente la eficiencia y el rendimiento [30]

[31]. A pesar de su robustez frente al multitrayecto en canales móviles, los sistemas OFDM

son susceptibles a errores de frecuencia, lo que ha impulsado la investigación en arquitecturas

de receptor con estimadores de frecuencia y fase para mitigar estos problemas y mejorar el

rendimiento del sistema.

## 2.1.1.1. Beneficios de la modulación OFDM en comunicaciones inalámbricas

OFDM es una técnica de modulación y multiplexación que se ha vuelto especialmente vital en sistemas de comunicación 4G como Wi-Fi, WiMAX y LTE, ya que proporciona altas velocidades de transmisión con interferencias mínimas [32]. OFDM reduce la distorsión multitrayecto

y las interferencias de frecuencia, lo que la hace ideal para redes CDMA y mejora el acceso inalámbrico en redes 4G [33].

Hassan, en su libro [34], presenta ciertas ventajas de un sistema de transmisión inalámbrico que utiliza OFDM:

- Los efectos del multitrayecto pueden ser contrarrestados utilizando OFDM, ya que esta modulación divide el espectro en varias subportadoras. De este modo, los desvanecimientos rápidos no afectan significativamente la información debido a los efectos del canal. Esto se debe a que dentro de esas subportadoras pueden introducirse portadoras piloto, que se utilizan para ecualizar el efecto del canal.

- OFDM se caracteriza por utilizar subportadoras ortogonales en frecuencia, lo cual se consigue mediante la transformada de Fourier. Esta característica permite un uso eficiente del ancho de banda, al posibilitar la superposición de portadoras ortogonales.

- Utilizar la Transformada Discreta de Fourier, lo que permite aumentar la tasa de bits, ya que posibilita incrementar el número de símbolos de premodulación antes de aplicar la IDFT en la etapa de modulación.

# 2.1.1.2. Modelo en Bloques del Sistema de Transmisión OFDM

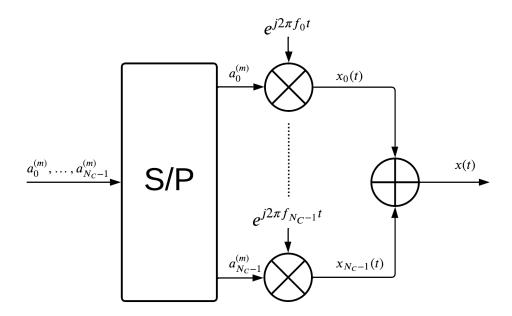

El principio de la multiplexación por división de frecuencias ortogonales (OFDM) consiste en ubicar símbolos modulados  $a_k^{(m)}$  en subportadoras ortogonales. Formalmente, la expresión para OFDM básico, sin prefijo cíclico y dentro del intervalo  $(mT_u \le t \le (m+1)T_u)$  [1], se describe como:

$$x(t) = \sum_{k=0}^{N_c - 1} x_k(t) = \sum_{k=0}^{N_c - 1} a_k^{(m)} e^{j2\pi k\Delta ft}$$

(2.1)

Donde,

- $x_k$ : Corresponde a la k-ésima subportadora modulada con frecuencia  $f_k = k \cdot \Delta f$ , [1].

- a<sub>k</sub><sup>(m)</sup>: Es el símbolo modulado que será ubicado en la k-ésima subportadora durante el m-ésimo intervalo de símbolos OFDM, [1].

- $T_u$ : Es el tiempo de símbolo de modulación por subportadora, [1].

- N<sub>c</sub>: Cantidad de moduladores complejos, también determina la cantidad de símbolos modulados.

- $\Delta f$ : Es el espaciado entre subportadoras y está definido como:  $\Delta f = 1/T_u$  [1].

La Figura 2.1 ilustra visualmente el funcionamiento básico de un modulador OFDM, mismo que corresponde a la representación gráfica de la Ecuación 2.1, [1].

Figura 2.1: Principio fundamental de la modulación OFDM. Fuente: [1].

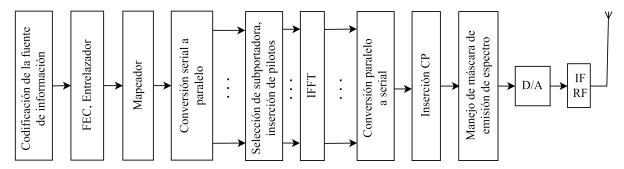

El proceso de modulación OFDM comienza con la conversión de bits, que corresponden a la fuente de información (*Information source encoding*), en símbolos modulados. Para realizar este procedimiento de premodulación se utilizan modulaciones digitales como QPSK o M-QAM. Esta conversión la realiza el bloque *Mapper*. Dado que la modulación OFDM se utiliza en comunicaciones inalámbricas móviles por su robustez frente a los efectos del canal variable, es necesario incluir una etapa de entrelazamiento para contrarrestar los efectos del desvanecimiento selectivo en frecuencia y evitar largas cadenas de bits con el mismo valor. Esta acción la realiza el bloque *Interleaver* [2].

Una vez terminado el proceso de entrelazamiento y premodulación, se procede a realizar una conversión de serial a paralelo (*bloque S/P*) de cada uno de los símbolos modulados. Luego de la etapa de paralelización, generalmente se insertan símbolos piloto que serán utilizados para estimar el comportamiento del canal o en la etapa de sincronización en el receptor. Posteriormente, los símbolos modulados se ubican en subportadoras ortogonales utilizando el algoritmo de la IFFT (*bloque IFFT*). Para controlar las emisiones fuera de banda, es necesario aplicar un prefijo cíclico (*CP insertion*). Adicionalmente, se puede incluir una etapa de filtrado para cumplir con la máscara de emisión espectral (SEM) [2]. Finalmente, la señal digital modulada se convierte en una señal analógica en banda base mediante el bloque (*D/A*). La señal analógica pasa por un proceso de amplificación y acoplamiento en radio frecuencia (RF) para

**U**CUENCA

ser radiada al aire.

El funcionamiento completo del transmisor OFDM se puede observar en la Figura 2.2 a continuación.

Figura 2.2: Diagrama de bloques de un sistema transmisor típico para una modulación OFDM. Fuente: [2].

# 2.1.1.3. Problemas Asociados con OFDM

Aunque OFDM se considera una opción adecuada para redes de banda ancha en frecuencias milimétricas, surge un desafío significativo debido a la demanda de los usuarios de latencia ultrabaja, que está vinculada a la sincronización y la ortogonalidad, elementos esenciales de OFDM [35]. Se sugiere adoptar un enfoque asincrónico que podría ser más prometedor que depender de algoritmos de sincronización avanzados, ya que estos últimos consumen más recursos de espectro y potencia [36] [3].

La necesidad de una trama más corta es crucial debido a las restricciones de tiempo críticas. En este contexto, la duración de símbolo de 67 microsegundos en OFDM de acuerdo al estándar LTE-A no parece ser una solución prometedora según [36].

Una modulación basada en *Orthogonal Frequency Division Multiplexing* (OFDM) presenta dos complicaciones notables que están directamente asociadas a su ventaja de ortogonalidad. La primera complicación ocurre si la señal presenta desfases o desplazamientos de frecuencia entre las subportadoras, comprometiendo así la ortogonalidad y la superposición de subportadoras [34]. La segunda complicación también afecta la ortogonalidad de las subportadoras, ya que para mantener esta ortogonalidad es necesario conservar una elevada relación de Potencia Pico a Promedio (PAPR). Sin embargo, mantener un valor de PAPR elevado requiere que el sistema cuente con dispositivos con un amplio rango lineal. Dado que el amplificador de potencia es un componente no lineal en el transmisor, podría causar la degradación del sistema [34].

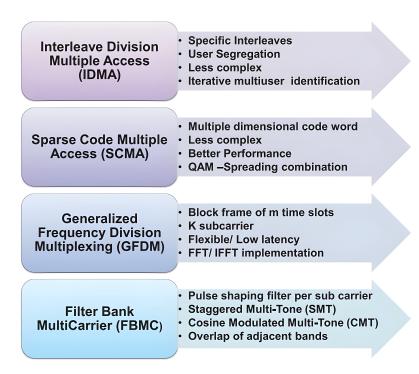

# 2.1.2. Técnicas avanzadas de acceso múltiple para 5G

En el libro 5G Mobile Communications [37], se ha propuesto que la nueva capa física en las comunicaciones 5G se adapte a conceptos innovadores como la Multiplexación por División de Frecuencia Generalizada (GFDM) o la Multiportadora de Banco de Filtros (FBMC) [38]. La modulación GFDM es considerada una posible candidata debido a su estructura de bloques que agrupan intervalos de tiempo y subportadoras para el envío de información [36]. Esta modulación se caracteriza por su flexibilidad, ya que puede ajustarse a los requisitos de baja latencia. Inclusive se ha propuesto algoritmos FFT/IFFT para la implementación de GFDM en [39]. Por otro lado, la Multiportadora de Banco de Filtros (FBMC) es considerada esencial para la capa *Media Access Control (MAC)* emergente en 5G [40].

Los sistemas multiportadora son caracterizados por su filtro formador de pulso, por lo que para el caso de FBMC se utiliza un filtro diseñado para localizar mejor a las subportadoras [41]. Métodos como *Staggered Multi-Tone* (SMT) y *Cosine modulated Multi-Tone* (CMT) son fundamentales en FBMC para maximizar la eficiencia del ancho de banda [41] [42]. SMT emplea *QAM offset* y CMT utiliza modulación de amplitud de pulsos para la transmisión de símbolos. Ambos permiten la superposición de bandas adyacentes para optimizar la eficiencia del ancho de banda.

En la Figura 2.3 se resumen las principales características de las nuevas propuestas de acceso múltiple para la quinta generación de redes móviles [3].

La 5ta Generación de redes móviles requiere que los patrones de haces espaciales deseables puedan garantizar fácilmente el acceso múltiple por división espacial (SDMA). Es necesario seguir investigando, no solo en SDMA, sino también en SCMA, IDMA, FBMC y GFDM para lograr baja latencia y alto rendimiento en las futuras redes 5G [3].

# 2.1.2.1. Generalized Frequency Division Multiplexing: GFDM

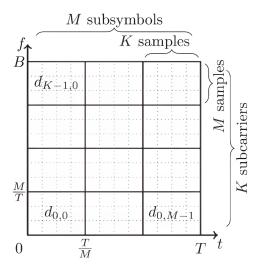

GFDM, a diferencia de OFDM, contiene un mayor espaciamiento en frecuencia y una mejor eficiencia energética, lo que la hace idónea en comunicaciones móviles 5G. Estas características de GFDM se deben a la optimización del modelo del filtro del pulso, de tal forma que son eficientes en canales con desvanecimiento selectivo de frecuencia [43]. Otra característica principal de GFDM es establecer una estructura bidimensional para la transmisión de símbolos, en la cual estos representan información a transmitir del usuario. La estructura bidimensional de GFDM se visualiza en la Figura 2.4, la cual consiste en la distribución de símbolos en

Figura 2.3: Acceso múltiple para la tecnología del futuro. Fuente: [3] © 2016 IEEE

instantes de tiempo y subportadoras. Esto se logra mediante, una convolución circular de un filtro formador de pulsos. Mediante ésta estructura se obtiene una mayor eficiencia espectral y flexibilidad sobre una implementación.

Figura 2.4: Partición del tiempo y la frecuencia GFDM. Fuente: [4] © 2014 IEEE

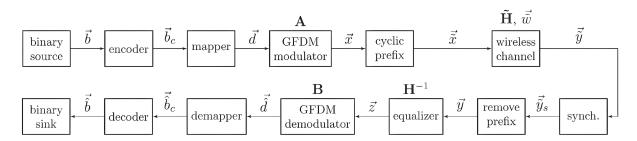

La Figura 2.5 muestra un esquema simplificado de un sistema de comunicaciones *Generalized Frequency Division Multiplexing (GFDM)*. En él se observa cómo los símbolos pertenecientes a una constelación QAM son obtenidos a partir de una fuente de información. Posteriormente, cada uno de los símbolos son mapeados a una subportadora y a un sub-símbolo (Figura 2.4). Tras definir la posición de cada uno de los símbolos, estos se transmiten a través de un filtro

formador de pulsos, como se muestra en la Figura 2.6. Finalmente, se agrega un prefijo cíclico a la señal resultante para evitar la interferencia intersímbolo. En el receptor, se debe ejecutar el proceso inverso al del sistema de transmisión. Además, el efecto del canal depende de las condiciones a las que se someten el sistema transmisor y receptor. Si se considera el caso de un canal móvil, tanto el transmisor como el receptor deben implementar medidas para mitigar los efectos de desvanecimiento.

Figura 2.5: Sistemas de comunicaciones GFDM. Fuente: [4] © 2014 IEEE

Figura 2.6: Modulador GFDM. Fuente: [4] © 2014 IEEE

Dentro de las investigaciones para GFDM se encuentra el uso recurrente de MIMO (*Multiple-Input Multiple-Output*). En [44], se ha explorado la integración de la técnica de modulación espacial (SM) con la Multiplexación por División de Frecuencia Generalizada (GFDM). La contribución principal de dicho trabajo radica en la creación de la estructura del sistema SM-GFDM y la evaluación de su *Bit Error Rate* (BER) en canales con desvanecimiento multitrayecto de Rayleigh.

La tecnología de transmisión de múltiples entradas y múltiples salidas (MIMO) es esencial para lograr velocidades de transmisión de datos más altas y una mayor eficiencia espectral [45]. La implementación de la transmisión MIMO involucra métodos, tales como, la codificación espacio-tiempo (STC), el espacio-tiempo por capas de Bell Labs (BLAST) y la modulación espacial (SM). STC busca maximizar la diversidad espacial para mejorar la eficiencia energética [46], [47]. Por otro lado, BLAST aumenta la capacidad transmitiendo múltiples flujos de datos independientes desde distintas antenas de transmisión. Variantes ampliamente utilizadas de BLAST incluyen BLAST diagonal (D-BLAST) [48] y BLAST vertical (V-BLAST) [49]. En el caso de SM, se utilizan los índices de antena de transmisión para llevar información adicional [50]. En este método, los bits de entrada determinan el punto de constelación en el conjunto de señales y el índice de la antena de transmisión activada. Durante cada intervalo de transmisión, la antena seleccionada transmite el símbolo elegido, mientras que las demás antenas permanecen en silencio, evitando así interferencias entre antenas (IAI) y la necesidad de sincronización entre antenas (IAS) [44].

Es esencial que cualquier propuesta de capa física destinada a redes inalámbricas 5G sea capaz de integrar la transmisión MIMO. Por lo tanto, existen estudios que exploran la modulación espacial (SM) en GFDM. Al combinar SM con GFDM, es posible desarrollar un sistema MIMO-GFDM que ofrece una flexibilidad significativa en la partición de tiempo y frecuencia, una baja emisión fuera de banda (OOB), una mejora en la eficiencia espectral y una sincronización flexible, todo ello sin incrementar significativamente la complejidad del sistema [44]. En [4], se muestra el detalle matemático de un sistema que implementa codificación de espacio-tiempo (STC) para dos antenas transmisoras y receptoras con GFDM. En el análisis se consideran canales selectivos de frecuencia, en los cuales el tiempo de coherencia del canal es mayor que el tiempo de símbolo de GFDM. Los resultados obtenidos establecen que GFDM, al contener una mejor resolución espectral por subportadora, permite una mejor ecualización en el dominio de la frecuencia, provocando que el SER (Symbol Error Rate) de STC-GFDM sea menor a STC-OFDM. En [51], se propone un esquema FDMA capaz de compartir subportadoras de una señal TR-STC (Time Reversal Space Time Coding) en GFDM entre múltiples usuarios. Con ello, a partir del conocimiento del estado del canal, se pueden asignar los subcanales disponibles a los usuarios, dando como resultado una mejora significativa en el rendimiento del SER (Symbol Error Rate). Por otro lado, en [52] y [53], se examina un sistema MIMO que utiliza multiplexación espacial y modulación GFDM, proponiendo esquemas de detección casi óptimos. Asimismo, en [54], se realiza el primer intento de aplicar la técnica de modulación espacial (SM) a un sistema MIMO-GFDM. Sin embargo, para evitar la auto interferencia entre portadoras (ICI) en GFDM, se limita la transmisión a un solo símbolo por bloque GFDM, lo que resulta en una eficiencia espectral considerablemente inferior en comparación con las implementaciones convencionales.

# 2.2. Sistemas de Radio definidos por Software: SDR

La radio definida por software (SDR) representa un avance significativo en las comunicaciones inalámbricas, permitiendo la personalización y optimización de sistemas de manera sencilla y eficiente. A diferencia de los radios tradicionales de hardware fijo, los SDR utilizan una arquitectura flexible que combina hardware reconfigurable con software, proporcionando una versatilidad notable [55]. Esta tecnología innovadora permite que un único dispositivo opere en múltiples bandas de frecuencia, maneje diversos esquemas de modulación y se adapte a distintos estándares de comunicación, lo cual a marcando un antes y después en el ámbito de las telecomunicaciones [56].

La flexibilidad y facilidad de actualización que caracterizan a los SDR se traducen en un control preciso sobre los componentes de procesamiento de señales digitales, incluyendo mezcladores, filtros, moduladores y demoduladores [56]. Esto abre un abanico de posibilidades para el desarrollo de aplicaciones personalizadas y soluciones a medida.

Los últimos avances en el campo de la SDR han dado lugar a arquitecturas reconfigurables que minimizan el consumo de energía, la latencia y los costes, abordando así los retos que anteriormente limitaban su adopción generalizada [57]. Estas nuevas arquitecturas combinan componentes genéricos de radio con microcontroladores de bajo consumo y coprocesadores especializados, permitiendo la transmisión de audio de alta definición en tiempo real con un consumo energético mínimo y una latencia imperceptible. Este avance tecnológico facilita la adopción de sistemas SDR de próxima generación, promoviendo la innovación en sectores como la telefonía móvil, las comunicaciones de datos, la radiodifusión y la investigación científica.

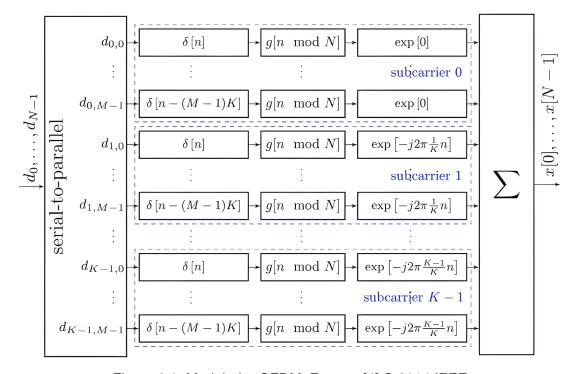

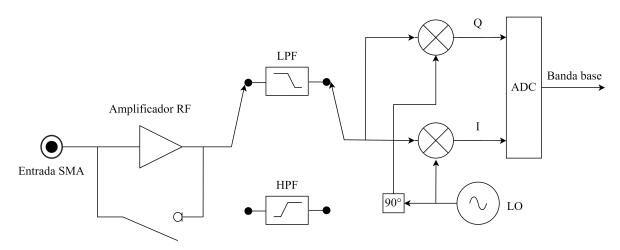

La Figura 2.7 muestra el diagrama de bloques de un receptor SDR. En este diagrama, una señal de radiofrecuencia es recibida por la antena y procesada por el bloque (RF Tuner). Este bloque consiste en un amplificador RF seguido de un mezclador analógico que recibe las señales del amplificador y un oscilador local de frecuencia variable, garantizando así una señal modulada a una frecuencia intermedia (IF). El bloque (Tuner) opera de manera similar a un receptor superheterodino [5].

Después de demodular la señal a una frecuencia intermedia, se procede a convertir la señal analógica en una señal digital utilizando un convertidor ADC. Como se muestra en la figura, el siguiente paso es procesar la señal utilizando un *Digital Down Converter (DDC)*, compuesto por un mezclador, un oscilador y un filtro paso bajo de tipo FIR, todos ellos componentes digitales. Este proceso de conversión descendente digital es lo que caracteriza a un sistema SDR. El objetivo final del DDC es convertir la señal de pasa banda a banda base [5]. El bloque final constituye un *Digital Signal Processor (DSP)* que se encarga de procesar la señal de acuerdo con los requisitos del usuario.

Figura 2.7: Diagrama de bloques del receptor SDR. Fuente: [5].

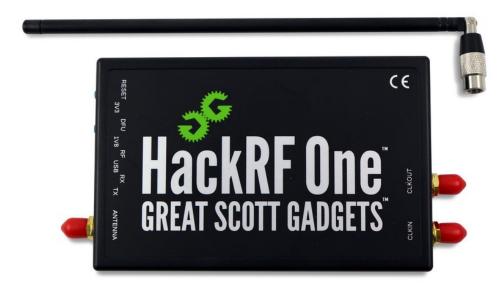

## 2.2.1. HackRF One

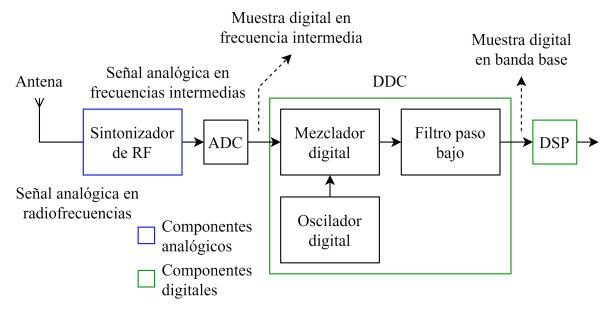

El dispositivo HackRF One mostrado en la Figura 2.8, desarrollado por Great Scott Gadgets, implementa tecnología *Software Defined Radio* (SDR) para la recepción de señales de radio-frecuencia. HackRF One es una herramienta de hardware de código abierto que es utilizado como un periférico mediante el bus de comunicaciones USB, es capaz de transmitir o recibir señales de radio de 1 MHz a 6 GHz [58].

El funcionamiento básico del dispositivo HackRF One se ilustra en la Figura 2.9. Primero, la señal RF es captada por una antena receptora con un puerto de entrada SMA. Dado que esta señal suele ser débil, se requiere amplificación para mejorar su potencia, por lo que pasa por una etapa de amplificación RF con una ganancia de 14 dB [7]. La señal amplificada no está exenta de componentes de alta frecuencia no deseadas. Para eliminarlas, se emplea un bloque *Low Pass Filter (LPF)* con una frecuencia de corte variable. Este filtro actúa como

una barrera selectiva, permitiendo el paso de las frecuencias de interés mientras bloquea las restantes. A continuación, la señal filtrada es procesada por medio de un mezclador en cuadratura junto a un oscilador local. Este proceso genera dos señales de banda base: una en fase (I) y otra en cuadratura (Q) [7].

Las señales I y Q se suman y luego se convierten en una señal digital de 8 bits por cada canal mediante un convertidor analógico-digital (ADC). Finalmente, la señal digital en banda base se entrega al usuario para su posterior procesamiento. Esta señal digitalizada contiene la información de la señal RF original, ahora en un formato que puede ser analizada.

Figura 2.8: Dispositivo HackRF One. Fuente: [6].

Figura 2.9: Diagrama de bloques del lado receptor del HackRF One. Fuente: [7].

# **U**CUENCA

## 2.2.2. GNU Radio

GNU Radio es un conjunto de herramientas de desarrollo de software libre y de código abierto, utilizado para crear aplicaciones de procesamiento de señales en tiempo real, especialmente en sistemas de comunicación inalámbricos, y diseñado para funcionar en ordenadores mono placa de bajo coste [15] [59].

GNU Radio proporciona una interfaz gráfica basada en bloques con un marco backend en Python, lo que permite a los usuarios redefinir los sistemas de comunicación predefinidos al modificar su programación en Python [60].

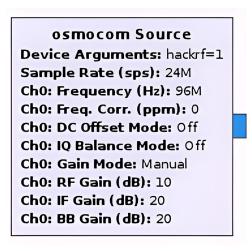

Para establecer la comunicación entre GNU Radio y el dispositivo HackRF One, se utiliza el bloque predefinido osmocom source, como se muestra en la Figura 2.10. Este bloque permite definir el tipo de dispositivo SDR que se utilizará, además de modificar parámetros clave como la frecuencia de muestreo y la frecuencia portadora.

Figura 2.10: Bloque Osmocom de GNU-RADIO. Fuente: [8]

# 2.3. Field Programmable Gate Array

Un Field Programmable Gate Array (FPGA) es un circuito integrado que permite al diseñador de hardware configurar la lógica y las interconexiones sin necesidad de intervención del fabricante, facilitando así la implementación de una variedad de circuitos digitales [61]. A diferencia de los Circuitos Integrados de Aplicación Específica (ASICs), las FPGAs ofrecen un ciclo de diseño más sencillo, permiten una creación de diseños más rápida mediante el uso de Lenguajes de Descripción de Hardware (HDL), y tienen tiempos de fabricación más cortos lo que facilita el prototipado. Estas características las hacen altamente flexibles y les proporcionan

altas velocidades de procesamiento [62].

Las FPGAs están formadas por bloques lógicos configurables organizados en una matriz, con funciones lógicas y conexiones definidas por celdas SRAM. Debido a la naturaleza volátil de la SRAM, estas celdas requieren reconfiguración cada vez que el dispositivo se enciende [63].

Las plataformas de desarrollo FPGA disponibles en la Universidad de Cuenca son: Spartan 3E, Basys 3 y STEMlab 125-14. A continuación, se presentan las características técnicas más relevantes de cada una.

# 2.3.1. Características técnicas de los dispositivos FPGA

La información relevante sobre las especificaciones técnicas de las plataformas FPGA disponibles en la Universidad de Cuenca se presenta en la Tabla 2.1. Las propiedades evaluadas con "Si/No" indican la presencia o ausencia de la característica específica en las tarjetas FPGA.

Tabla 2.1: Características técnicas de los dispositivos FPGA. Fuentes: [9] [19] [20] [10] [11] [21]

| Tarjeta<br>FPGA   | Hardware<br>RF | Internal<br>Clock | DAC | Laboratorio | LUTs  | Flip<br>Flop | IDE           |

|-------------------|----------------|-------------------|-----|-------------|-------|--------------|---------------|

| Spartan 3E        | No             | 50 MHz            | 12  | No          | 9312  | 9312         | ISE<br>Design |

| Basys 3           | No             | 100 MHz           | No  | No          | 20800 | 41600        | Vivado        |

| STEMlab<br>125-14 | Si             | 125 MHz           | 14  | Si          | 17600 | 35200        | Vivado        |

# 2.3.2. Spartan 3E

La tarjeta Spartan 3E presentada en la Figura 2.11 es un dispositivo FPGA programable de tipo XC3S500E que cuenta con 500,000 puertas lógicas y un procesador RISC de 32 bits [9]. La tarjeta utiliza el IDE ISE Design Suite para realizar su programación de descripción de hardware. Sin embargo, ISE ya no cuenta con soporte del fabricante Xilinx (hoy bajo AMD). Sus características específicas se presentan en la Tabla 2.1.

Figura 2.11: Dispositivo FPGA Spartan 3E. Fuente: [9]

# 2.3.3. Basys 3

La tarjeta Basys 3 mostrada en la Figura 2.12 es una herramienta de desarrollo muy útil para el aprendizaje de las FPGA, ya que cuenta con cuatro puertos de 16 pines digitales cada uno. Está equipada con una FPGA de alta capacidad XC7A35T-1CPG236C de Xilinx basada en la FPGA Artix 7 [10], lo que proporciona una arquitectura poderosa para la programación de circuitos complejos y su respectiva depuración. La Tabla 2.1 presenta un resumen de las características técnicas de la tarjeta Basys 3.

Figura 2.12: Dispositivo FPGA Basys 3. Fuente: [10]

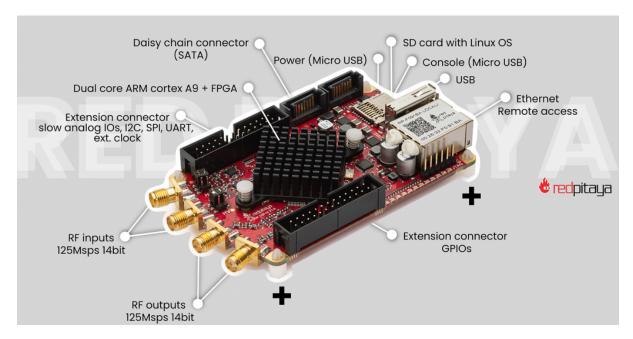

#### 2.3.4. STEMlab 125-14

El dispositivo STEMlab 125-14 de la empresa Red Pitaya presentada en la Figura 2.13, es una tarjeta con mejores prestaciones en comparación con otras tarjetas FPGA como las mencionadas arriba. Además de contar con una FPGA Xilinx Zynq 7010, también incluye un sistema operativo Linux que se ejecuta sobre un procesador Dual-Core ARM Cortex-A9 MPCore [11]. Esto permite interactuar con herramientas de laboratorio, como un osciloscopio y un analizador de espectros, que están integradas en el dispositivo. Un resumen de las características de la tarjeta FPGA se muestran en la Tabla 2.1.

Figura 2.13: Dispositivo FPGA STEMlab 125-14. Fuente: [11]

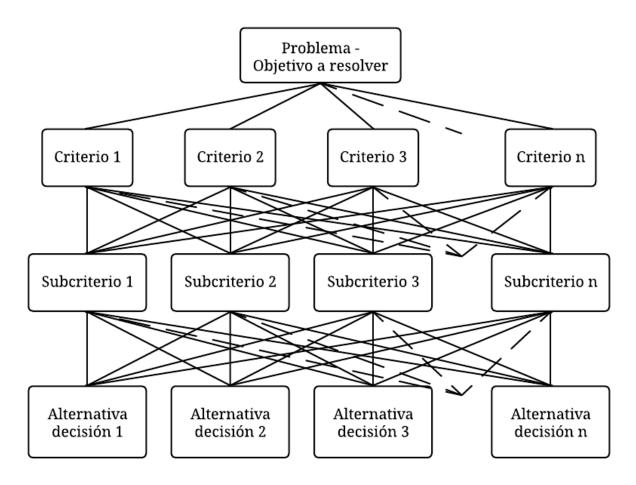

# 2.4. Método Analytic Hierarchy Process

Para seleccionar la tarjeta FPGA adecuada para el desarrollo del trabajo de integración curricular, se utilizará el método *Analytic Hierarchy Process* (AHP) de Thomas Saaty. Este método permitirá comparar las tres opciones de tarjetas FPGA y tomar una decisión basada en siete criterios de selección.

El profesor Thomas L. Saaty creó el Proceso Analítico Jerárquico (*Analytic Hierarchy Process*, AHP) en los años 70 y 80 como técnica de toma de decisiones multicriterio, donde se utilizan comparaciones por pares para determinar escalas de prioridad [64] [65]. El AHP es útil en tareas de toma de decisiones y clasificación porque transforma las evaluaciones subjetivas en ponderaciones, lo que ayuda a elegir soluciones para situaciones complicadas [66]. Debido a la naturaleza humana, permite la derivación de escalas de relación a partir de comparaciones por pares, teniendo en cuenta pequeñas discrepancias en los juicios. Como marco para la resolución de problemas, el AHP divide las tareas en segmentos manejables y utiliza comparaciones directas por pares para determinar el orden de importancia dentro de cada jerarquía [67]. La claridad y practicidad de este enfoque metódico quedan demostradas por su valor en la toma de decisiones que abarcan costes, oportunidades, riesgos y recompensas.

# 2.4.1. Metodología del Análisis Jerárquico AHP

El *Analytical Hierarchy Process* (AHP) utiliza una escala de juicios absolutos para realizar la comparación entre opciones, permitiendo tratar las inconsistencias en los juicios para mejorar la coherencia. La metodología se puede utilizar para tomar decisiones complejas en una variedad de áreas, desde la administración pública hasta la distribución de recursos en grandes empresas [12].

Para realizar un análisis AHP de manera efectiva, Thomas Saaty en [12] sugiere seguir los siguientes pasos:

- 1. **Definición del problema y planteamiento del objetivo:** Definir claramente el problema que se pretende abordar y el alcance del análisis AHP, se considera como el objetivo a la solución del problema de decisión, por tanto debe ser específico, medible y alcanzable.

- Estructuración de la jerarquía de decisión: La jerarquía debe descomponerse en niveles jerárquicos claros, empezando con el objetivo general, luego los criterios y subcriterios hasta terminar con las posibles opciones de decisión.

# 3. Comparaciones pareadas

- Escala para las comparaciones pareadas: Las comparaciones en pares deben realizarse utilizando una escala de comparación estándar, como la escala fundamental de Saaty, la cual se presenta con mayor detalle en la Sección 2.4.3.

- Consistencia: Verificar la consistencia de las comparaciones utilizando métodos como el índice de consistencia (CI) y la razón de consistencia (CR).

- 4. Determinación de las escalas de prioridad: A cada criterio y subcriterio se le debe asignar un valor numérico que represente su importancia relativa dentro de su nivel jerárquico.

- 5. **Priorización de las alternativas:** Cálculo de la ponderación final al realizar la combinación del valor numérico de cada criterio o subcriterio en función de cada alternativa de solución.

# 2.4.2. Estructuración de los niveles de jerarquía

El proceso AHP es descompone el problema en una jerarquía de decisiones que consiste en:

- Objetivo principal: La meta última que se desea alcanzar.

- Criterios: Factores o atributos que influirán en la decisión.

- Subcriterios (Opcional): Desgloses más detallados de los criterios principales.

- Alternativas: Opciones entre las cuales se debe elegir.

La Figura 2.14 muestra gráficamente el resultado de la descomposición en jerarquía del problema a analizar.

# 2.4.3. Escala fundamental de Saaty

Tras establecer la jerarquía de decisión, se procede a realizar comparaciones pareadas entre los elementos de cada nivel. Para ello, se utiliza la escala de importancia desarrollada por Thomas Saaty, la cual asigna valores numéricos del 1 al 9 para representar la intensidad de la importancia relativa entre dos elementos. En esta escala, el valor 1 indica que los elementos son de igual importancia, mientras que el valor 9 representa la máxima diferencia en importancia entre dos elementos. La Tabla 2.2, que se presenta a continuación, muestra la escala fundamental de Comparación de Saaty.

Figura 2.14: Estructura jerárquica del método AHP. Fuente: [12]

Tabla 2.2: Escala fundamental de Saaty. Fuente: [22]

| Nivel de<br>Importancia | Definición                      | Explicación                                                                                                                                                                                                      |

|-------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                       | Igualmente<br>importante        | Ambos criterios poseen igual importancia                                                                                                                                                                         |

| 3                       | Moderadamente<br>más importante | Un criterio es ligeramente más importante que otro                                                                                                                                                               |

| 5                       | Fuertemente<br>más importante   | Considerable importancia de un criterio sobre otro                                                                                                                                                               |

| 7                       | Extremadamente más importante   | Evidencia extrema importancia de un criterio sobre otro                                                                                                                                                          |

| 9                       | Absolutamente<br>más importante | Orden de importancia con el valor más alto posible                                                                                                                                                               |

| 2,4,6,8                 | Valores intermedios             | Importancia media entre niveles adyacentes                                                                                                                                                                       |

| $a_{ij} = 1/a_{ji}$     | Recíprocos                      | Cuando el valor del criterio en la fila $i$ en relación con el criterio en la columna $j$ es igual a un entero de los mencionados anteriormente, entonces el valor de $j$ en relación con $i$ es igual a $1/a$ . |

# 2.4.4. Matrices de comparación y cálculo de prioridades

Cada elemento de la matriz cuadrada de comparaciones pareadas representa una comparación individual entre dos criterios o alternativas del mismo nivel jerárquico. Cada elemento de la matriz tiene un valor numérico que muestra la intensidad de la preferencia relativa entre los dos elementos que se comparan. La Tabla 2.2 muestra la escala Saaty que sirve como base para estos valores. Posteriormente, se calculan los vectores de prioridad utilizando la información de las matrices de comparaciones pareadas. Estos vectores asignan un peso ponderado a cada criterio o alternativa, representando la importancia relativa de cada elemento en su nivel jerárquico. La Tabla 2.3 a continuación muestra un ejemplo de aplicación.

|            | Criterio 1 | Criterio 2 | Criterio 3 |   | Criterio n |

|------------|------------|------------|------------|---|------------|

| Criterio 1 | 1          | а          | b          |   | c          |

| Criterio 2 | 1/a        | 1          | 1/d        |   | 1/e        |

| Criterio 3 | 1/b        | d          | 1          |   | 1/f        |

| ÷          | :          | :          | :          | ٠ | :          |

| Criterio n | 1/c        | e          | f          |   | 1          |

Tabla 2.3: Ejemplo de Matriz de Comparación Pareada.

# 2.4.5. Consistencia del Análisis

En el contexto de la toma de decisiones multicriterio mediante el Proceso Analítico Jerárquico (AHP), es fundamental asegurar la coherencia lógica en la jerarquía de prioridades, lo cual se logra a través de un análisis de consistencia [68]. El método AHP utiliza dos herramientas matemáticas, el Índice de Consistencia (CI) y el índice de Consistencia Aleatoria (RC), para evaluar y mejorar la consistencia en las comparaciones por pares [69] [70].

El CI es un indicador numérico que mide el nivel de inconsistencia en las comparaciones por pares y el tamaño de la jerarquía [71]. Para determinar el índice de consistencia CI es necesario definir la matriz cuadrada de *n* criterios **M** como:

$$\mathbf{M} = \begin{bmatrix} M_{11} & M_{12} & \cdots & M_{1n} \\ M_{21} & M_{22} & \cdots & M_{2n} \\ \vdots & \vdots & \ddots & \vdots \\ M_{n1} & M_{n2} & \cdots & M_{nn} \end{bmatrix}$$

(2.2)

Luego, es necesario determinar el valor del vector de ponderación correspondiente a la valoración de cada criterio, donde se requiere calcular la matriz normalizada E de valores, nor-

malizando cada columna de la matriz de criterios. El proceso de normalización se lleva a cabo dividiendo cada elemento de una columna por la suma de todos los elementos de dicha columna.

Formalmente, si  $M_{ij}$  representa el elemento en la fila i y columna j de la matriz original M, entonces el elemento  $e_{ij}$  de la matriz normalizada E se calcula como:

$$e_{ij} = \frac{\mathbf{M_{ij}}}{\sum_{k=1}^{n} \mathbf{M_{ki}}}$$

(2.3)

Donde,  $\sum_{k=1}^{n} \mathbf{M_{kj}}$  es la suma de todos los elementos de la columna j. Los elementos  $e_{ij}$  forman la matriz normalizada E.

$$\mathbf{E} = \begin{bmatrix} e_{11} & e_{12} & \cdots & e_{1n} \\ e_{21} & e_{22} & \cdots & e_{2n} \\ \vdots & \vdots & \ddots & \vdots \\ e_{n1} & e_{n2} & \cdots & e_{nn} \end{bmatrix}$$

(2.4)

Ahora para determinar el vector de valores ponderados es necesario calcular el promedio por filas de la matriz normalizada, y como resultado se obtiene el vector de pesos  $\vec{b}$ .

$$\vec{b}_i = \frac{1}{n} \sum_{i=1}^n e_{ij} \tag{2.5}$$

Una vez se posee la matriz de cuadrada de criterios M y el vector de ponderación  $\vec{b}$ , entonces es posible calcular el índice de consistencia (CI), que corresponde a:

$$CI = \frac{n_{max} - n}{n - 1} \tag{2.6}$$

Donde:

- $n_{max}$ : Es el resultado de la combinación lineal de la matriz **M** por el vector de ponderación  $\vec{b}$ .

- n : Cantidad de criterios utilizados por el método AHP.

Por otra parte, la relación de consistencia (CR) compara el valor del índice de consistencia (CI) con un Índice Aleatorio (RI) obtenido de tablas predefinidas, lo que permite a los responsables de la toma de decisiones evaluar la consistencia de las comparaciones y tomar decisiones bien fundamentadas [72]. La Tabla 2.4 muestra la referencia según [23] que será utilizada para determinar el valor del índice RI.

| Tabla 2.4: Tabla de referencia | oara el índice de consistencia | aleatorio. Fuente: [23] | 1 |

|--------------------------------|--------------------------------|-------------------------|---|

|                                |                                |                         |   |

| n                                           | 1 | 2 | 3    | 4   | 5    | 6    | 7    | 8    | 9    | 10   |

|---------------------------------------------|---|---|------|-----|------|------|------|------|------|------|

| Índice de<br>Consistencia<br>Aleatorio (RI) | 0 | 0 | 0.58 | 0.9 | 1.12 | 1.24 | 1.32 | 1.41 | 1.45 | 1.49 |

El valor de **n** en la Tabla 2.4 corresponde al número de criterios que será utilizados por el análisis AHP.

Por último, se calcula la relación de consistencia CR de la forma:

$$CR = \frac{CI}{RI} \tag{2.7}$$

Para que una relación de consistencia sea considerada aceptable es necesario que cumpla la condición de  $CR \le 0.1$ .

### 2.4.6. Síntesis de Prioridades

La síntesis que corresponde al último paso de un proceso AHP, consiste en combinar las prioridades locales (ponderaciones de criterios y subcriterios) para obtener las prioridades globales de las alternativas. Este proceso se realiza mediante una sencilla multiplicación, donde la prioridad global de una alternativa se calcula como la suma de los productos entre su desempeño en cada criterio y la ponderación correspondiente de ese criterio.

### 2.5. Trabajos Relacionados

En este apartado se revisan trabajos e investigaciones previas sobre la implementación de sistemas de transmisión multiportadora en plataformas FPGA. El objetivo es analizar el estado del arte, identificar las técnicas y metodologías más utilizadas, y comprender los retos abordados en estudios anteriores. Cabe mencionar el trabajo presentado en [73] y desarrollado en la Universidad de Cuenca, en el que se utiliza una plataforma FPGA basada en un SPARTAN-3E de Xilinx, para el desarrollo de un sistema de comunicaciones digitales. En ese trabajo se explora diferentes técnicas de modulación digital de portadora simple, y que en parte ha motivado el desarrollo del presente trabajo de integración curricular. A continuación mencionaremos algunos trabajos relacionados en el contexto de sistemas multiportadora.

En [74], se llevó a cabo la implementación de un sistema de comunicación OFDM mediante el uso de una plataforma FPGA con un modelo de punto-fijo. Este sistema se desarrolló mediante la construcción de bloques funcionales basados en el modelo matemático OFDM utilizando una modelización inicial del sistema en la plataforma Matlab y, posteriormente, la implementación apoyada de Xilinx System Generator for DSP (XSG) y Simulink. El diseño se fundamentó en el estándar IEEE 802.11a y se implementó en una tarjeta de desarrollo Xilinx Virtex-5. Para verificar el desempeño del sistema OFDM, se empleó la técnica de co-simulación de hardware, que ofrece una forma eficiente de validar y evaluar su rendimiento. El sistema se sometió a pruebas utilizando un enfoque de hardware en bucle, permitiendo el cálculo y la comparación de la tasa de error de bits (BER) en relación a los resultados del modelo realizado en Matlab. Los resultados demuestran la correcta implementación del sistema OFDM en banda base, ya que el transmisor requiere 15.6µs para generar las primeras muestras de la señal OFDM. Sin embargo, se observa una degradación del BER debido a que, con un SNR alto, se pierde precisión al representar niveles de ruido débil en el modelo de punto fijo implementado en la FPGA.

Por otra parte, en [75] se presenta el diseño y desarrollo de un sistema OFDM utilizando el lenguaje de programación VHDL. La implementación de este sistema se llevó a cabo en una tarjeta de desarrollo FPGA Virtex-6. El proceso de diseño involucró la creación y simulación del sistema OFDM con modulación 64-QAM. Su implementación se fundamentó en el procesamiento de señales digitales de alta velocidad, haciendo uso de módulos IFFT/FFT. Para verificar la precisión de los resultados, se realizaron simulaciones en MATLAB, lo que permitió la comparación entre los resultados obtenidos en dichas simulaciones y aquellos generados por Xilinx ISE. Estos resultados demuestran la correcta implementación de OFDM en FPGA, ya que la señal generada se asemeja a la simulación realizada en MATLAB en el dominio de la frecuencia. La verificación y validación del hardware se completaron a través del empleo del kit FPGA Xilinx Virtex-6.

El modelo matemático y la operación base de GFDM se presentan en [76] y [77]. En el estudio [76], se implementan los esquemas de modulación y demodulación GFDM en el simulador Vienna 5G. Su aporte consiste en desarrollar un ecualizador en el dominio del tiempo enfocado en canales desvanecimiento (Fading), cuya idea principal es dividir el canal en sub-bloques para luego promediarlos. Para encontrar el número de sub-bloques que minimizan el *Bit Error Rate* (BER), se utilizan algoritmos genéticos para optimizar los modelos de regresión que predicen el BER del sistema. Los resultados demuestran que el esquema GFDM implementado y su ecualización superan la tasa de error de otras modulaciones, tales como OFDM. Por otra

parte, en [77] se proponen técnicas de multiplexación espacial para GFDM mediante el uso de un modelo lineal acotado en el que solo se considera la influencia del ruido Gaussiano. Los resultados demuestran que GFDM no es un reemplazo general para OFDM, dado que presenta una mayor complejidad y un rendimiento variable en la demodulación de GFDM. Por tanto, se propone que GFDM puede ser utilizado en escenarios con selectividad en frecuencia, siendo apto para aplicaciones especializadas de radio móvil (SMR), radio cognitiva (CR) y comunicación ultra confiable de baja latencia (URLLC).

En [78], se realiza una implementación de GFDM sobre una plataforma FPGA. Esta implementación utiliza el software NI PXI y el módulo LabView FPGA con el objetivo de realizar una prueba de concepto de un transmisor GFDM. Por lo tanto, sus resultados son preliminares, ya que se limitan a mostrar la forma de onda y el espectro de potencia de la señal GFDM generada por la FPGA, sin realizar ningún tipo de verificación adicional.

Finalmente, una implementación de GFDM se encuentra disponible en GNU Radio [79]. Esta representa una implementación de radio definida por software (SDR), la cual proporciona información detallada sobre cómo aprovechar la flexibilidad de SDR para simulaciones y pruebas en campo. Esta implementación también permite la integración de interfaces con otros lenguajes de programación. Además, este estudio realizó una prueba de campo que consistió en una transmisión inalámbrica, donde el procesamiento de señales se llevó a cabo en una computadora portátil con un hardware Intel Core i7-6700HQ y 16 GB de RAM. Los resultados de esta transmisión demuestran la correcta modulación y demodulación de GFDM, utilizando aproximadamente el 90% de un núcleo del *Central Processing Unit* (CPU) con una frecuencia de muestreo de 3.125*MHz*. Sin embargo, al aumentar la frecuencia de muestreo de la señal, se requiere el uso de más de un núcleo del CPU, llegando a necesitar aproximadamente 3 núcleos con una frecuencia de muestreo de 25*MHz*.

### Desarrollo del Sistema

En este capítulo se realiza el análisis AHP para seleccionar la tarjeta más adecuada para el proyecto. Se describe la implementación del sistema de transmisión multiportadora, detallando el funcionamiento de cada uno de sus bloques. Finalmente, se desarrolla el módulo receptor utilizado para evaluar el sistema de transmisión.

# 3.1. Análisis de los dispositivos FPGA disponibles en la Universidad de Cuenca