# UNIVERSIDAD DE CUENCA

# Facultad de Ingeniería

Carrera de Electrónica y Telecomunicaciones

Implementación y análisis de algoritmos de sincronización de fase, para fuentes de energía renovables en sistemas trifásicos

Trabajo de titulación previo a la obtención del título de Ingeniero en Electrónica y Telecomunicaciones.

## Autores:

Andrés Antonio Segovia Vásquez C.I: 110449514-6 andres4058@gmail.com

# Director:

Ing. Luis Gerardo González Morales, PhD

C.I: 010390703-6

Cuenca – Ecuador 26 de julio de 2021

# Resumen

Con la finalidad de lograr que dos o más fuentes externas estén sincronizadas entre sí y evitar daños en dispositivos finales; se han desarrollado algoritmos de sincronización que trabajen en conjunto con sistemas de electrónica de potencia y sistemas de control, que permitan sensar la señal de las Renewable Energy Sources (RES), para establecer de forma correcta los parámetros necesarios para inyectar energía a la red principal. Con este preámbulo; el presente trabajo de titulación muestra la implementación, análisis y comparación de los algoritmos de sincronización que más utilizados en este campo; tomando como objeto de estudio aquellos que son lazo de bloque de fase:

- con marco de referencia síncrono (dqPLL)

- con marco de referencia estacionario (PLL)

- con doble desacople en el marco de referencia síncrono (DDSRF-PLL)

- con doble integrador generalizado de segundo orden (DSOGI-PLL).

Para el cumplimiento de objetivos y desarrollo de la investigación, fue necesaria la combinación de herramientas computacionales como PSIM® y el entorno de desarrollo integrado (Code Composer Studio (CCS)), además de un elemento de hardware como un Procesador Digital de Señales (Digital Signal Processor (DSP)), este último permite recolectar los datos por medio de los puertos del módulo convertidor A/D, posteriormente realiza el procesamiento de la señal ejecutando los algoritmos programados. Para la adquisición de datos se requiere de la implementación de un sistema de potencia que permita acoplar la señal de la red con los parámetros de entrada de los puertos que soportan el DSP.

La obtención de resultados se resume en una primera prueba en la que en modo de simulación se insertó una distorsión en frecuencia a la RES; y en una segunda prueba para resultados prácticos, con la utilización de paneles solares poli-cristalinos del laboratorio de micro red de Universidad de Cuenca; estas pruebas reflejan la eficiencia de cada algoritmo expuesto a las mismas fallas. Dichos antecedentes a su vez fueron resultado de la visualización de su comportamiento y funcionamiento (uso del osciloscopio del software PSIM, comunicación serial entre el DSP y la PC, puertos PWM del dispositivo).

Finalmente, mediante un proceso de conexión y desconexión de la RES, se observó el comportamiento y estabilidad de cada algoritmo al someterse a este tipo de perturbaciones, y se realizó una comparativa de las repuestas obtenidas, teniendo como parámetro principal el tiempo de establecimiento.

Palabras clave : RES. PSIM. DSP. CCS. Electrónica de potencia. Sistemas de Control. algoritmos de sincronización. lenguaje C++. Módulo convertidor A/D.

# **Abstract**

In order to achieve that two or more external electrical energy sources are synchronized with each other and prevent damage to end devices, synchronization algorithms have been developed that work in conjunction with power electronics systems and control systems that allow the detection of the power signal of the Renewable Energy Sources (RES) to correctly establish the necessary parameters to inject energy into the main network. With this preamble, the present degree work shows the implementation, analysis and comparison of the most used synchronization algorithms in this field, taking as object of study those that are phase block loops:

- Synchronous reference Frame (dqPLL)

- Stationary reference Frame ( $\alpha\beta$ -PLL)

- Double decoupling synchronous reference frame (DDSRF-PLL)

- Dual second-order generalized integrator (DSOGI-PLL).

In order to fulfill the objectives and development of the research, it was necessary to combine computational tools such as PSIM® and a integrated development environment )Code Composer Studio (CCS)) and a hardware element such as a Digital Signal Processor (DSP). The latter allows data to be collected through the ports of the A/D converter module, and to carry out signal processing by executing the programmed algorithms. Data acquisition requires the implementation of a power system that allows coupling the network signal with the input parameters of the ports that support the DSP.

The obtaining of results is summarized in a first test in which in simulation mode a frequency distortion was inserted at the RES; and in a second test for practical results, with the use of polycrystalline solar panels from the micro-grid laboratory of the University of Cuenca. These tests reflect the efficiency of each algorithm exposed to the same faults and disturbances. These antecedents in turn were the result of the visualization of its behavior and operation (use of the PSIM software oscilloscope, serial communication between the DSP and the PC, PWM ports of the device).

Finally, through a process of connection and disconnection of the RES, the behavior and stability of each algorithm when subjected to this type of disturbance was observed, and a comparison of the responses obtained was made with the establishment time as the main parameter.

Keywords: RES. PSIM. DSP. CCS. Power electronics. Control Systems. Synchronization Algorithms. C++ language. A/D converter module.

# **Índice** general

| Resu            | umen                                                                             | 1  |

|-----------------|----------------------------------------------------------------------------------|----|

| $\mathbf{Abst}$ | cract                                                                            | 2  |

| Índic           | ce general                                                                       | 3  |

| Índic           | ce de figuras                                                                    | 7  |

| Índic           | ce de tablas                                                                     | 11 |

| Cláu            | sula de Propiedad Intelectual                                                    | 12 |

| Cláu            | sula de licencia y autorización para publicación en el Repositorio Institucional | 13 |

| Cert            | ifico                                                                            | 14 |

| Dedi            | icatoria                                                                         | 15 |

| Agra            | adecimientos                                                                     | 16 |

| Abre            | eviaciones y acrónimos                                                           | 17 |

| 1. In           | ntroducción                                                                      | 18 |

| 1.              | 1. Introducción                                                                  | 18 |

| 1.5             | 2. Antecedentes                                                                  | 19 |

| 1.3             | 3. Alcance                                                                       | 19 |

| 1.              | 4. Objetivos                                                                     | 20 |

|                 | 1.4.1. Objetivo general                                                          | 20 |

|                 | 1.4.2. Objetivos específicos                                                     | 20 |

| 1.              | 5. Estructura del documento                                                      | 20 |

| 2. M            | farco Teórico                                                                    | 22 |

| 2.              | 1. Fuentes de Generación de Energía Eléctrica Renovables y No Renovables         | 22 |

|                 | 2.1.1. Fuentes de Generación de Energía no renovables                            | 23 |

|                 | 2.1.1.1. Petróleo                                                                | 23 |

|                 | 2.1.1.2. Carbón                                                                  | 23 |

|                 | 2.1.1.3. Gas Natural                                                             | 23 |

|                 | 2.1.1.4. Nuclear                                                                 | 24 |

|                 |                                                                                  |    |

|    |      | 2.1.2.  | Fuentes de Generación de Energía Renovables                                                    | 24        |

|----|------|---------|------------------------------------------------------------------------------------------------|-----------|

|    |      |         | 2.1.2.1. Hidráulica                                                                            | 24        |

|    |      |         | 2.1.2.2. Eólica                                                                                | 25        |

|    |      |         | 2.1.2.3. Solar                                                                                 | 25        |

|    |      |         | 2.1.2.4. Biomasa                                                                               | 25        |

|    | 2.2. | Estruc  | ctura de los Sistemas de Transmisión y Distribución Eléctricos                                 | 26        |

|    | 2.3. |         | tos Regulatorios para la Transmisión y Distribución de Energía Eléctrica                       | 28        |

|    |      | 2.3.1.  | Nivel de voltaje                                                                               | 29        |

|    |      | 2.3.2.  | Perturbaciones rápidas de voltaje (Flicker)                                                    | 29        |

|    |      | 2.3.3.  | Distorsión armónica de voltaje                                                                 | 29        |

|    |      | 2.3.4.  | Desequilibrio de voltaje                                                                       | 30        |

|    |      | 2.3.5.  | Frecuencia                                                                                     | 30        |

|    |      | 2.3.6.  | Sincronización                                                                                 | 30        |

|    |      | 2.3.7.  | Reconexión al sistema de potencia eléctrico                                                    | 30        |

|    | 2.4. | Algori  | tmos de Sincronización de Red                                                                  | 31        |

|    |      | _       | Detección de cruce por cero                                                                    | 31        |

|    |      | 2.4.2.  | Algoritmos de lazo de bloqueo de fase (PLL)                                                    | 31        |

|    |      |         | 2.4.2.1. Lazo de bloque de fase con marco de referencia síncrono (dqPLL)                       | 35        |

|    |      |         | 2.4.2.2. Lazo de bloque de fase con marco de referencia estacionario $(\alpha\beta\text{PLL})$ | 36        |

|    |      |         | 2.4.2.3. Lazo de bloqueo de fase con doble desacople en el marco de referencia                 |           |

|    |      |         | síncrono (DDSRF-PLL)                                                                           | 36        |

|    |      |         | 2.4.2.4. Lazo de bloqueo de fase con desacople en el marco de referencia esta-                 |           |

|    |      |         | cionario (DSRF-PLL)                                                                            | 39        |

|    |      |         | 2.4.2.5. Lazo de bloqueo de fase con doble integrador generalizado de segundo                  |           |

|    |      |         | orden (DSOGI-PLL)                                                                              | 39        |

|    | 2.5. | Compa   | aración de desempeño mediante herramienta computacional PSIM                                   | 40        |

|    | 2.6. | -       | sador digital de señales (DSP) TMDSCNCD28335                                                   | 41        |

|    |      |         | io creador de código (CCS)                                                                     | 41        |

|    |      | 25044   | 10 0700007 00 000000 (0 00)                                                                    |           |

| 3. | Dise | eño y l | Desarrollo Experimental                                                                        | <b>42</b> |

|    | 3.1. | Adqui   | sición de datos por medio del DSP                                                              | 42        |

|    |      | 3.1.1.  | Acondicionamiento de la señal para lectura del DSP                                             | 43        |

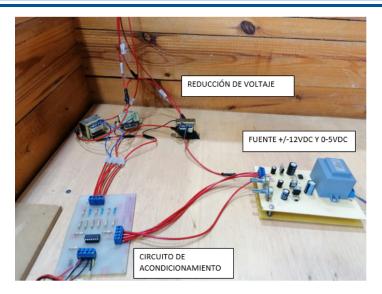

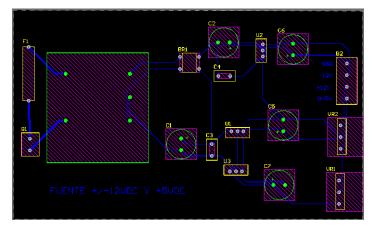

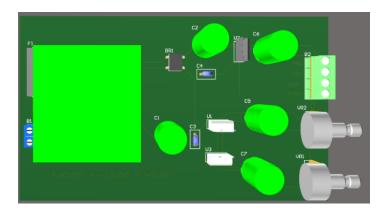

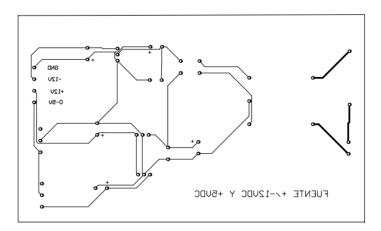

|    |      |         | 3.1.1.1. Diseño e implementación de la fuente simétrica                                        | 44        |

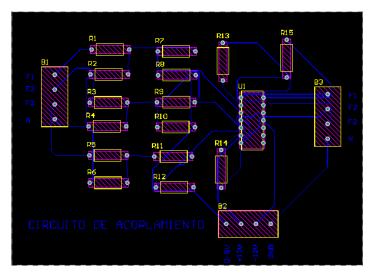

|    |      |         | 3.1.1.2. Diseño e implementación del circuito de acoplamiento                                  | 45        |

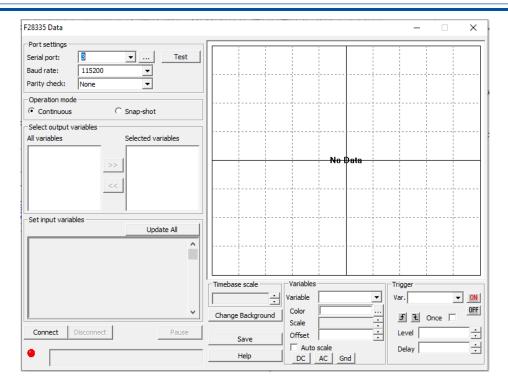

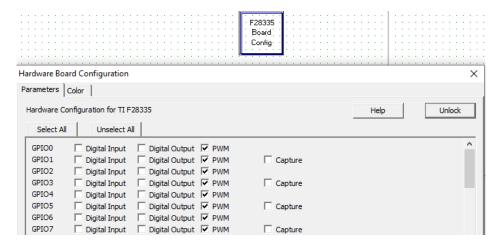

|    |      | 3.1.2.  | Configuración de PSIM                                                                          | 47        |

|    |      | 3.1.3.  | Generación de código C/C++                                                                     | 49        |

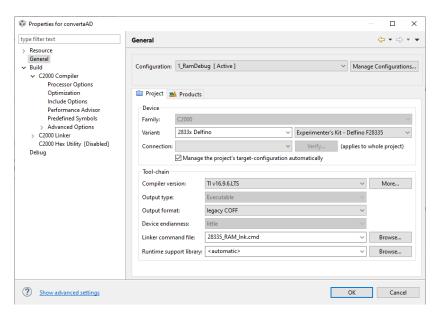

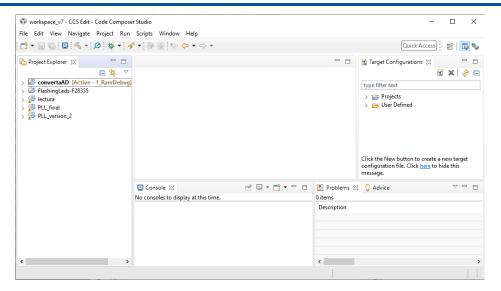

|    |      | 3.1.4.  | Configuración de Code Composer Studio (CCS)                                                    | 50        |

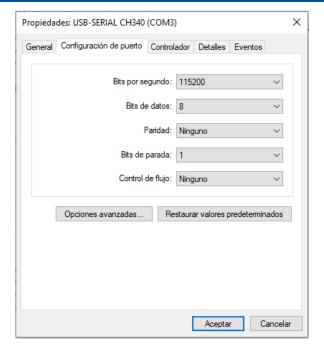

|    | 3.2. | Config  | guración del puerto serial para la visualización de datos por medio de la interfaz             |           |

|    |      | Serial  | Communication Interface (SCI)                                                                  | 50        |

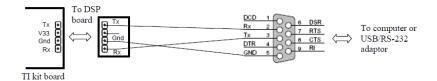

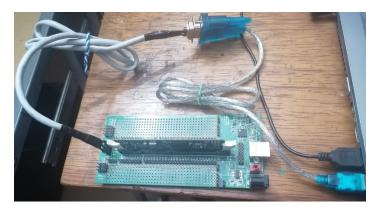

|    |      | 3.2.1.  | Diseño, Implementación y Configuración de la comunicación serial entre PC y DSP                | 50        |

|    |      | 3.2.2.  | Implementación de la conexión para la comunicación serial en PSIM $\dots$                      | 52        |

|    | 3.3. | Visual  | lización de datos                                                                              | 53        |

|    |      | 3.3.1.  | Utilizando el Osciloscopio de PSIM                                                             | 53        |

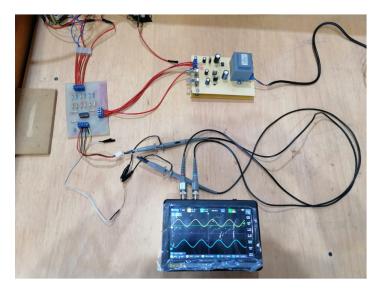

|    |      | 3.3.2.  | Utilizando el osciloscopio digital físico                                                      | 54        |

|    | 3.4. | Implementación de algoritmos de sincronización de fase                    | 55        |

|----|------|---------------------------------------------------------------------------|-----------|

|    |      | 3.4.1. Normalización de las señales de entrada                            | 56        |

|    |      | 3.4.2. Establecimiento de parámetros del Proporcional-Integral (PI)       | 56        |

|    |      | 3.4.3. Distorsión de frecuencia en la señal de entrada                    | 58        |

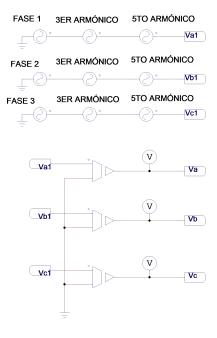

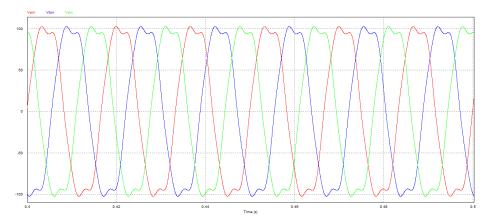

|    |      | 3.4.4. Distorsión armónica en la señal de entrada                         | 59        |

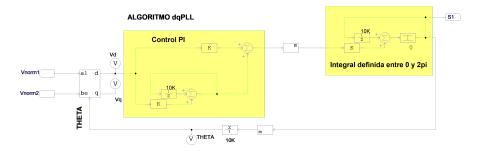

|    |      | 3.4.5. Diseño e implementación del algoritmo dqPLL                        | 60        |

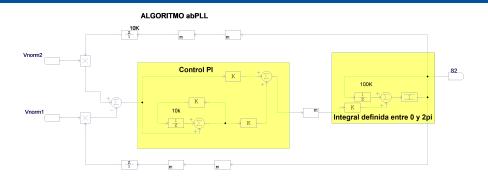

|    |      | 3.4.6. Diseño e implementación del algoritmo $\alpha\beta$ PLL            | 60        |

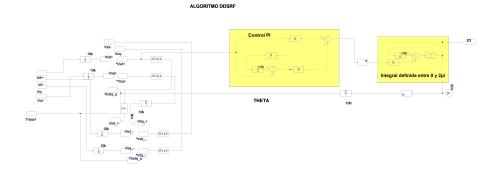

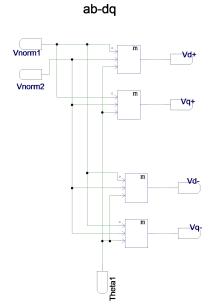

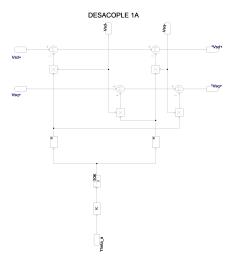

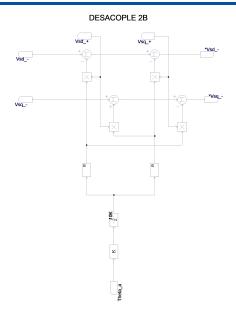

|    |      | 3.4.7. Diseño e implementación del algoritmo DDSRF-PLL                    | 61        |

|    |      | 3.4.8. Diseño e implementación del algoritmo DSOGI-PLL                    | 63        |

| 4. | Res  | ultados, Conclusiones y Recomendaciones                                   | <b>65</b> |

|    |      | · · · · · · · · · · · · · · · · · · ·                                     | 65        |

|    | 4.2. | 1 1                                                                       | 68        |

|    | 4.3. | ,                                                                         | 70        |

|    |      |                                                                           | 71        |

|    |      | 4.4.1. Distorsión en frecuencia                                           | 71        |

|    |      | 4.4.1.1. dq-PLL                                                           | 71        |

|    |      | 4.4.1.2. $\alpha\beta$ -PLL                                               | 71        |

|    |      | 4.4.1.3. DDSRF-PLL                                                        | 72        |

|    |      | 4.4.1.4. DSOGI-PLL                                                        | 72        |

|    |      | 4.4.2. Distorsión armónica                                                | 73        |

|    |      | 4.4.2.1. dq-PLL                                                           | 73        |

|    |      | 4.4.2.2. $\alpha\beta$ -PLL                                               | 73        |

|    |      | 4.4.2.3. DDSRF-PLL                                                        | 74        |

|    |      | 4.4.2.4. DSOGI-PLL                                                        | 74        |

|    |      | 4.4.3. Desconexión y Conexión de la fuente renovable                      | 75        |

|    |      | 4.4.3.1. dq-PLL                                                           | 75        |

|    |      | 4.4.3.2. $\alpha\beta$ -PLL                                               | 75        |

|    |      | 4.4.3.3. DDSRF-PLL                                                        | 76        |

|    |      |                                                                           | 77        |

|    | 4.5. | Análisis y discusión de los resultados                                    | 78        |

|    | 4.6. | v                                                                         | 79        |

|    |      |                                                                           | 79        |

|    |      |                                                                           | 80        |

|    | 4.7. | Trabajos futuros                                                          | 81        |

| Α. | Elal | boración del proyecto, diseño de componentes para fabricación de la PCB y |           |

|    | gene | eración del archivo .gerber en Altium                                     | <b>82</b> |

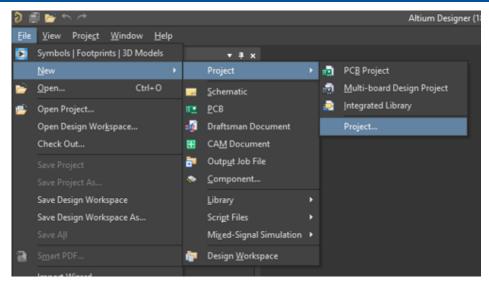

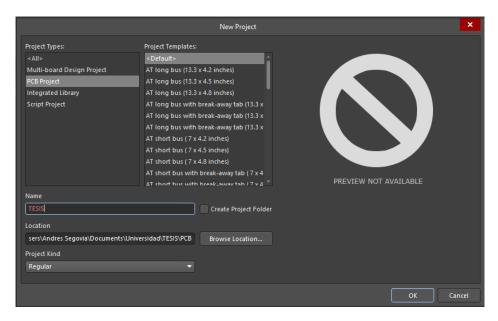

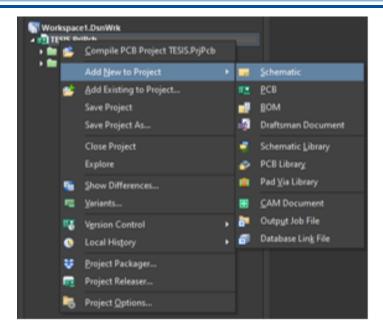

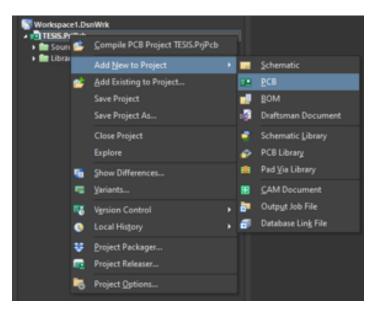

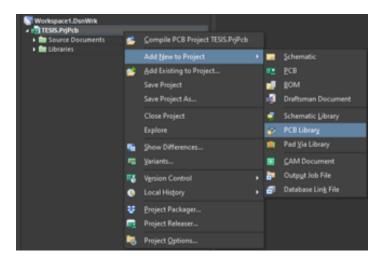

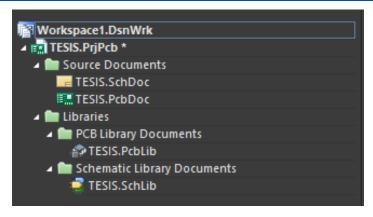

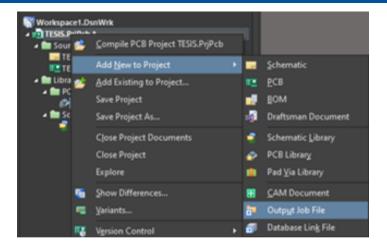

|    | A.1. | Elaboración del proyecto en Altium                                        | 82        |

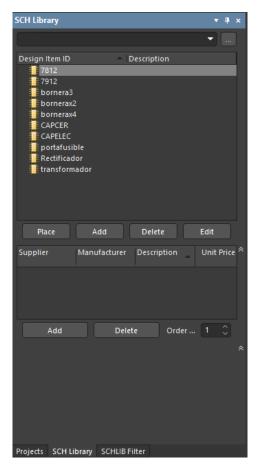

|    | A.2. | Diseño esquemático del elemento en Atium                                  | 86        |

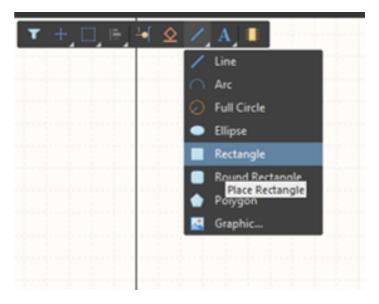

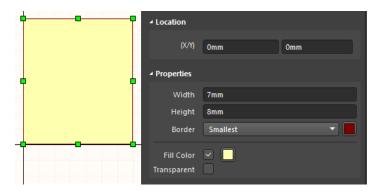

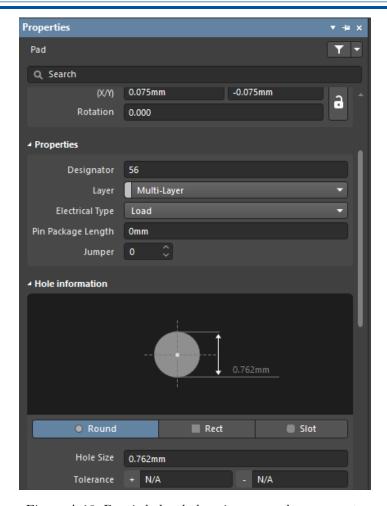

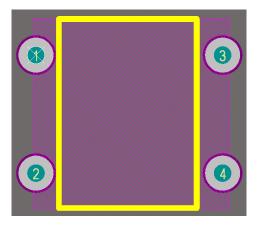

|    | A.3. | Diseño del footprint del componente en Altium                             | 89        |

|    | A.4. | Elaboración del archivo .Gerber                                           | 94        |

| B. Configuración de CCS                                                   | 104 |

|---------------------------------------------------------------------------|-----|

| B.1. Configuración de CCS para la importación del código generado en PSIM | 104 |

| B.2. Grabado del código en la tarjeta de control F28335                   | 107 |

| C. Código para la lectura de datos                                        | 110 |

| D. Código para el cálculo de los parámetros kp y Ti del controlador       | 116 |

| Bibliografía                                                              | 117 |

# Índice de figuras

| 2.1.  | Topología básica de conexión de fuentes renovables con la red principal [17]                                | 27 |

|-------|-------------------------------------------------------------------------------------------------------------|----|

| 2.2.  | Esquema de una sistema de Generación, Transmisión y Distribución de la red Eléctrica.                       |    |

|       | [20]                                                                                                        | 27 |

| 2.3.  | Estructura general de un Sistema Eléctrico [20] $\dots \dots \dots \dots \dots \dots \dots$                 | 28 |

| 2.4.  | Detección de cruce por cero de una señal senoidal ruidosa $[35]$                                            | 31 |

| 2.5.  | Diagrama de Bloques básico de un PLL                                                                        | 32 |

| 2.6.  | Topología básica de los PLL ([17]) $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$                           | 32 |

| 2.7.  | Diagrama de Bloques de un dqPLL [33] $\dots \dots \dots \dots \dots \dots \dots$                            | 35 |

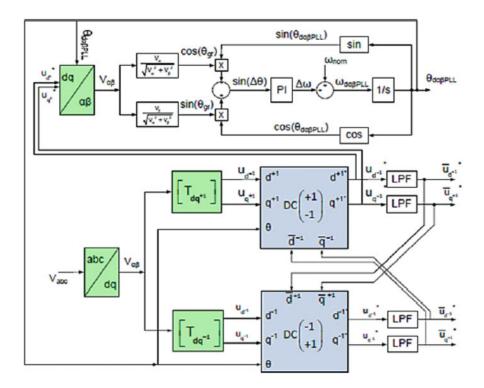

| 2.8.  | Diagrama de Bloques de un $\alpha\beta$ PLL [17]                                                            | 36 |

| 2.9.  | Diagrama de Bloques de un Decoupled Double Synchronous Reference Frame-Phase                                |    |

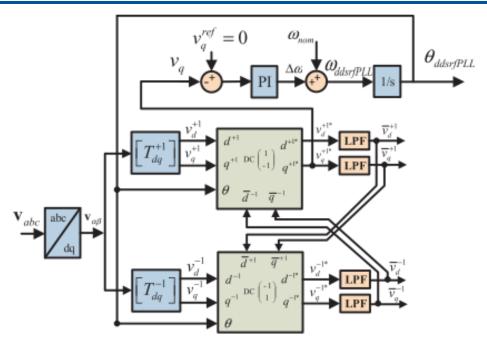

|       | Locked Loop (DDSRF-PLL) [17]                                                                                | 38 |

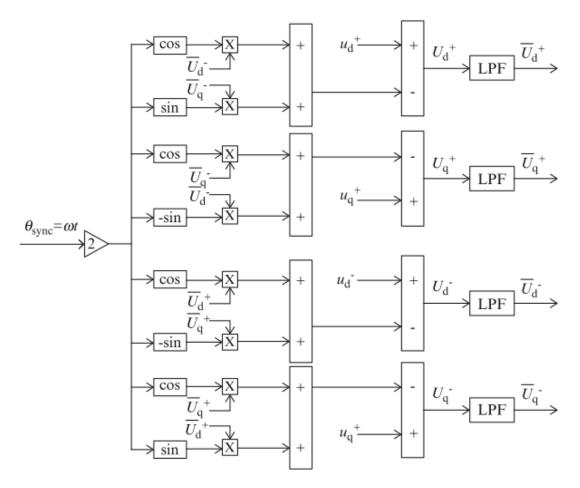

| 2.10. | . Red de desacoplamiento para secuencias positivas y negativas, utilizada en DSRF-PLL $[\overline{\bf 33}]$ | 38 |

| 2.11. | Diagrama de Bloques de un DSRF-PLL [44]                                                                     | 39 |

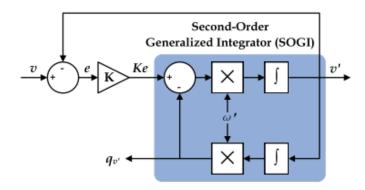

| 2.12. | Estructura de bloques del algoritmo SOGI [42]                                                               | 40 |

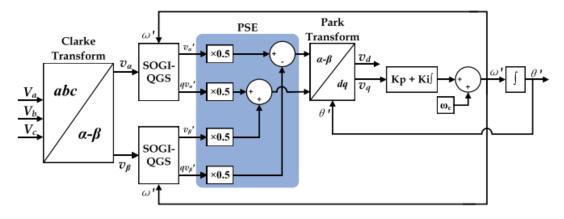

| 2.13. | Estructura de bloques del algoritmo DSOGI-PLL [42]                                                          | 40 |

| 2.14. | Placa (DSP) TMDSCNCD28335                                                                                   | 41 |

| 9.1   |                                                                                                             | 49 |

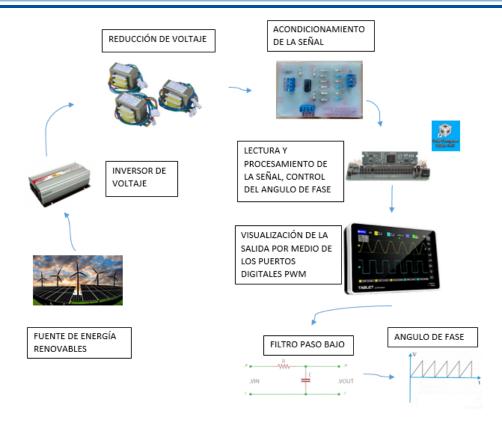

| 3.1.  | Estructura básica del funcionamiento del sistema de sincronización de fase                                  | 43 |

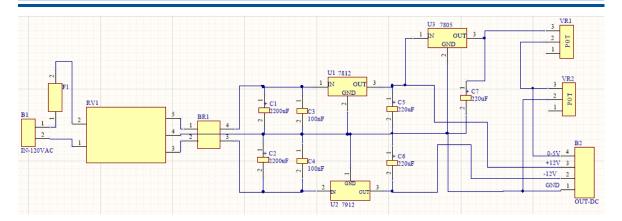

| 3.2.  | Circuito esquemático de la fuente de alimentación                                                           | 44 |

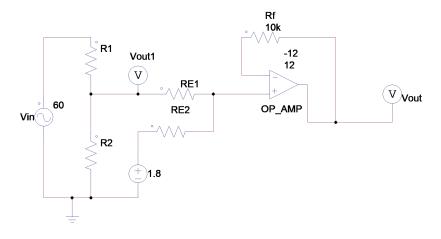

| 3.3.  | Circuito de acondicionamiento de señal                                                                      | 45 |

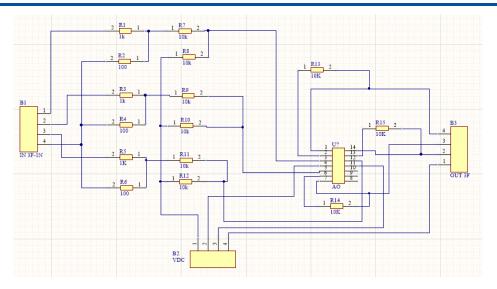

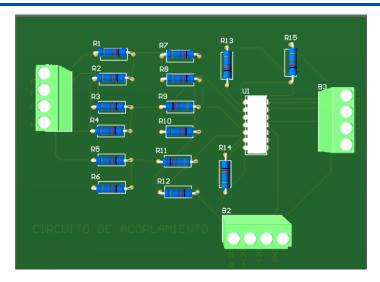

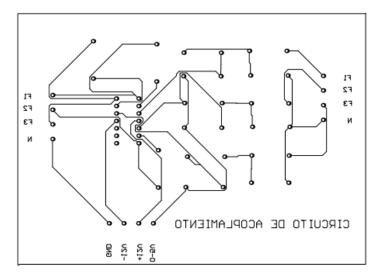

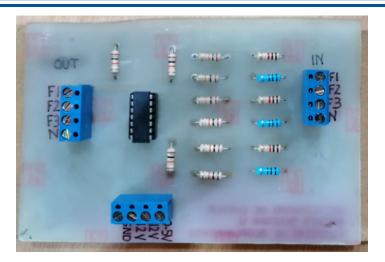

| 3.4.  | Diseño esquemático del circuito de acoplamiento                                                             | 47 |

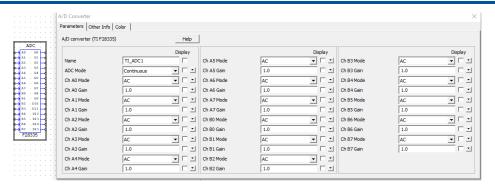

| 3.6.  | Bloque Convertidor Analógico/Digital de PSIM                                                                | 48 |

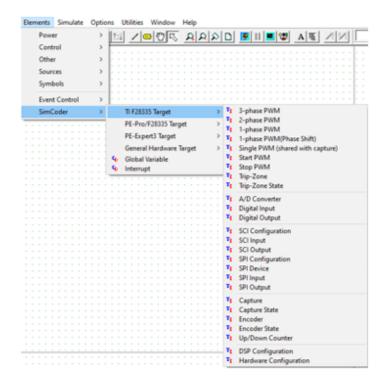

| 3.5.  | Librerías de PSIM para la tarjeta F28335                                                                    | 48 |

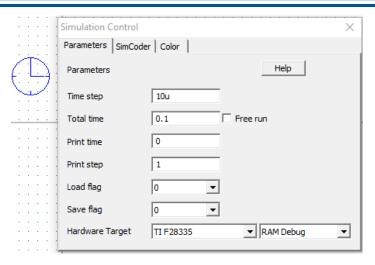

| 3.7.  | Configuración del control de simulación                                                                     | 49 |

| 3.8.  | Lectura de las señales de ingreso, para su análisis                                                         | 49 |

| 3.9.  | Configuración de CCS para la compilación y la exportación a la tarjeta                                      | 50 |

|       | Conexión de los puertos de la PC y DSP                                                                      | 51 |

|       | Diagrama de conexión entra la PC y el DSP                                                                   | 51 |

|       | Conexión física para la comunicación serial                                                                 | 51 |

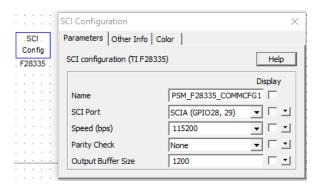

|       | Configuración del puerto de comunicación                                                                    | 52 |

|       | Configuración General para el módulo SCI                                                                    | 52 |

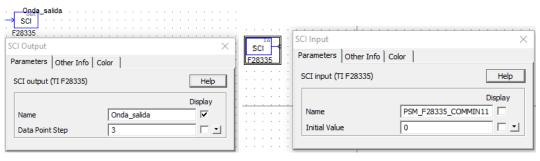

|       | Configuración de los módulos I/0 para la interfaz SCI                                                       | 53 |

|       | Interfaz de usuario del Osciloscopio                                                                        | 54 |

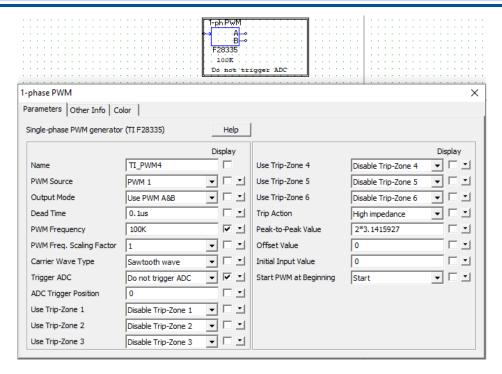

| 3.17. | Configuración de la tarjeta para el uso de los puertos digitales como PWM                                   | 54 |

|       |                                                                                                             |    |

| 3.18. Configuración de los parámetros del puerto PWM                                           | 55         |

|------------------------------------------------------------------------------------------------|------------|

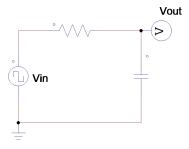

| 3.19. Circuito integrador como filtro paso bajo                                                | 55         |

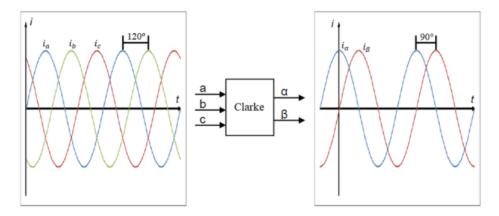

| 3.20. Paso de un sistema de coordenadas de 3 fases a un sistema estacionario ortogonal por     |            |

| medio de la transformada de Clarke                                                             | 56         |

| 3.21. Normalización de la señal trifásica, utilizando las componentes $\alpha\beta$            | 56         |

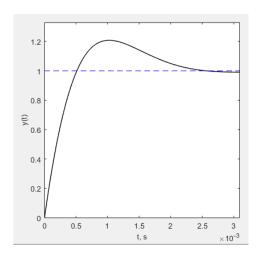

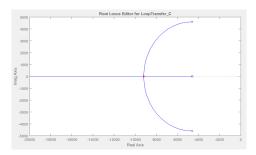

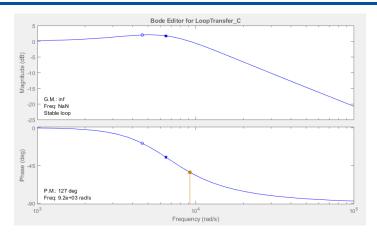

| 3.22. Respuesta al impulso del sistema con un tiempo de establecimiento de 3ms                 | 57         |

| 3.23. Raíces y Polos del sistema utilizados para análisis de estabilidad                       | 57         |

| 3.24. Diagrama de bode para análisis de estabilidad del sistema                                | 58         |

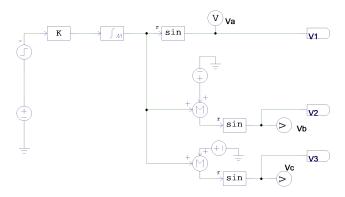

| 3.25. Sub-circuito para la distorsión de frecuencia en la simulación                           | 58         |

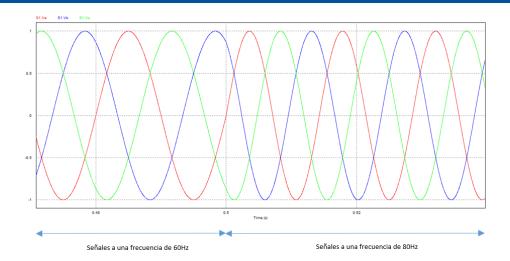

| 3.26. Respuesta de la distorsión de frecuencia para simulación                                 | 59         |

| 3.27. Distorsión armónica para las tres fases de entrada                                       | 59         |

| 3.28. Señales trifásicas con distorsión armónica                                               | 60         |

| 3.29. Esquema del algoritmo dq-PLL en PSIM                                                     | 60         |

| 3.30. Esquema del algoritmo $\alpha\beta$ PLL en PSIM                                          | 61         |

| 3.31. Esquema del algoritmo DDSRFPLL en PSIM                                                   | 61         |

| 3.32. Transformada $\alpha\beta$ a dq                                                          | 62         |

| 3.33. Esquema de desacople para la secuencia positiva                                          | 62         |

| 3.34. Esquema de desacople para la secuencia negativa                                          | 63         |

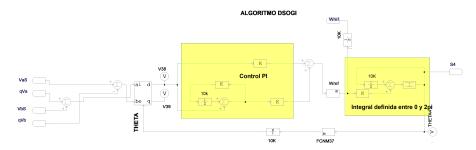

| 3.35. Esquema del algoritmo DSOGIPLL en PSIM                                                   | 63         |

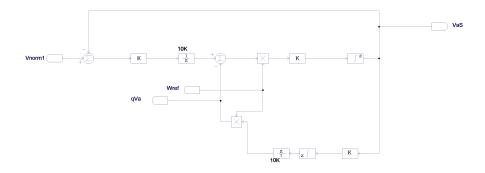

| 3.36. Esquema del algoritmo SOGI-PLL en PSIM para la fase $\alpha$                             | 64         |

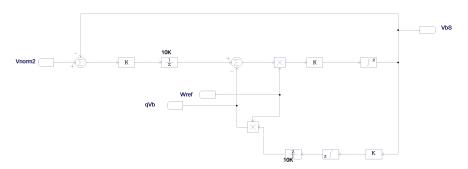

| 3.37. Esquema del algoritmo SOGI-PLL en PSIM para la fase $\beta$                              | 64         |

|                                                                                                |            |

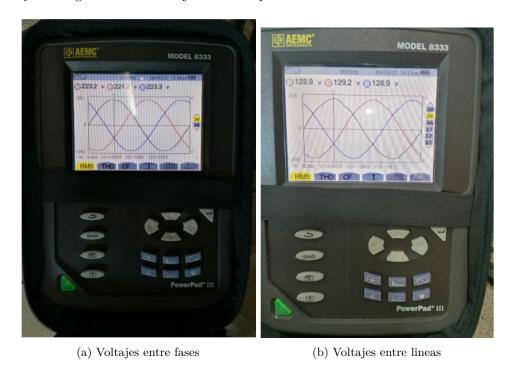

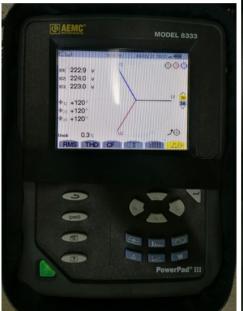

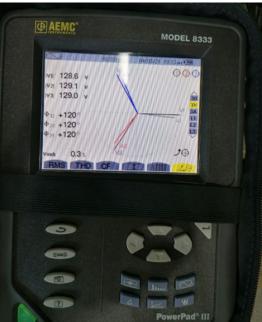

| 4.1. Tablero inversor para tensión de PANELES SOLARES POLI-CRISTALINOS                         | 66         |

| 4.2. Voltajes de salida del inversor para la entrada del circuito de acoplamiento              | 66         |

| 4.3. Ángulos de desfases de las señales de salida del inversor para la entrada del circuito de |            |

| acoplamiento                                                                                   | 67         |

| 4.4. Conexión al breaker principal de los transformadores                                      | 67         |

| 4.5. Conexión al circuito de acondicionamiento para el Digital Signal Processor (DSP)          | 68         |

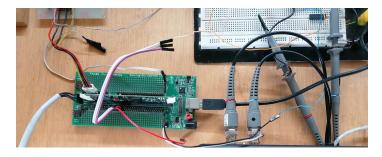

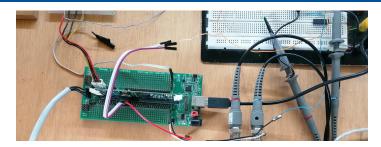

| 4.6. Conexión del Osciloscopio para las pruebas de la señal de entrada                         | 68         |

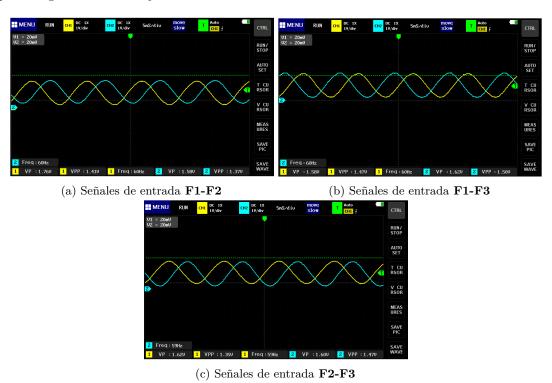

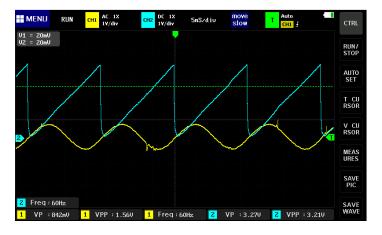

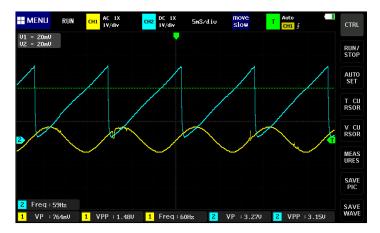

| 4.7. Señales de entrada al DSP tomadas a la salida del circuito de acondicionamiento           | 69         |

| 4.8. Señal trifásica de entrada en los puertos analógicos del DSP                              | 69         |

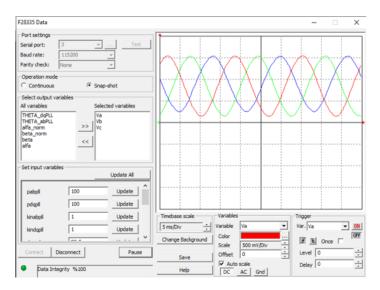

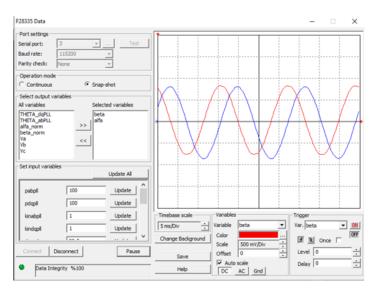

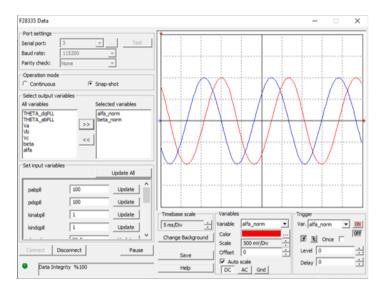

| 4.9. Componentes $\alpha\beta$ de la transformada de Clarke                                    | 70         |

| 4.10. Normalización de las componentes $\alpha\beta$ de la transformada de Clarke              | <b>7</b> 0 |

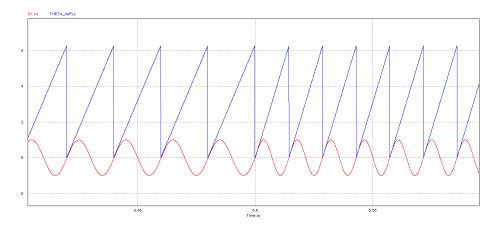

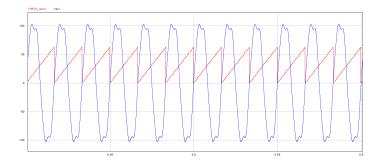

| 4.11. Respuesta del algoritmo dqPLL con distorsión de fase                                     | 71         |

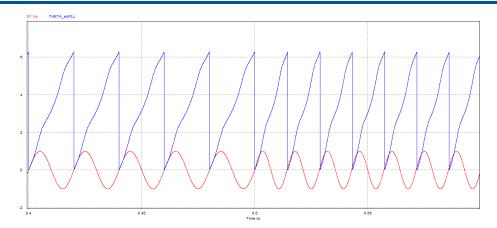

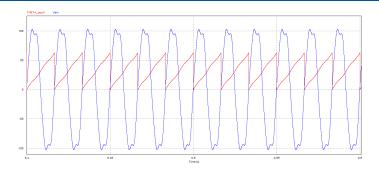

| 4.12. Respuesta del algoritmo $\alpha\beta$ PLL con distorsión de fase                         | 72         |

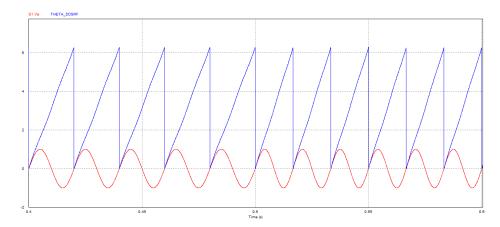

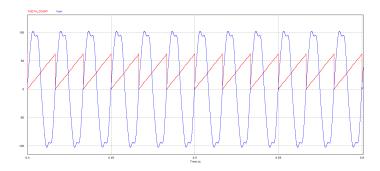

| 4.13. Respuesta del algoritmo DDSRFPLL con distorsión de fase                                  | 72         |

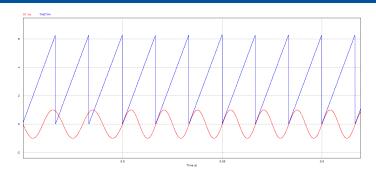

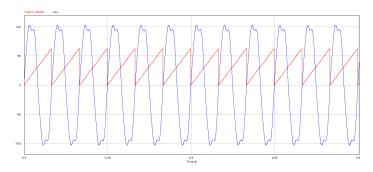

| 4.14. Respuesta del algoritmo DSOGI-PLL con distorsión de fase                                 | 73         |

| 4.15. Respuesta del algoritmo dq-PLL con presencia de armónicos                                | 73         |

| 4.16. Respuesta del algoritmo $\alpha\beta$ -PLL con presencia de armónicos                    | 74         |

| 4.17. Respuesta del algoritmo DDSRF-PLL con presencia de armónicos                             | 74         |

| 4.18. Respuesta del algoritmo DSOGI-PLL con presencia de armónicos                             | 74         |

| 4.19. Esquema de conexión para la captura de datos del algoritmo dq-pll                        | 75         |

| 4.20. Respuesta del algoritmo dq-PLL con los paneles solares                                   | 75         |

| 4.21. Esquema de conexión para la captura de datos del algoritmo $\alpha\beta$ -PLL            | <b>7</b> 6 |

| 4.22. Respuesta del algoritmo $\alpha\beta$ -PLL con los paneles solares   | ; |

|----------------------------------------------------------------------------|---|

| 4.23. Esquema de conexión para la captura de datos del algoritmo DDSRF-PLL | ; |

| 4.24. Respuesta del algoritmo DDSRF-PLL con los paneles solares            | 7 |

| 4.25. Esquema de conexión para la captura de datos del algoritmo DSOGI-PLL | 7 |

| 4.26. Respuesta del algoritmo DSOGI-PLL con los paneles solares            | 3 |

|                                                                            |   |

| A.1. Dirección para la creación de un nuevo proyecto                       |   |

| A.2. Configuración de la dirección y nombre del proyecto                   |   |

| A.3. Añadir archivo esquemático en el proyecto                             |   |

| A.4. Añadir archivo PCB en el proyecto                                     |   |

| A.5. Añadir archivo esquemático para librería en el proyecto               |   |

| A.6. Añadir archivo PCB para librería en el proyecto                       |   |

| A.7. Archivos añadidos al proyecto                                         |   |

| A.8. Propiedades para los archivos esquemáticos de las librerías           |   |

| A.9. Añadir y configurar nombre del componente                             |   |

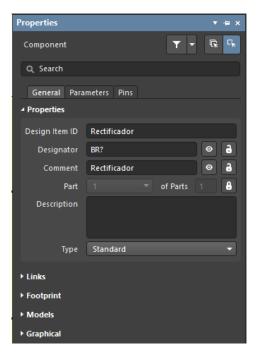

| A.10.Crear superficie del componente                                       |   |

| A.11.Propiedades de diseño del componente                                  | 7 |

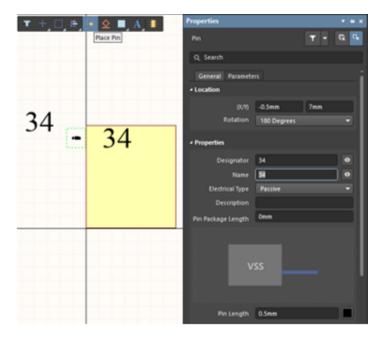

| A.12.Añadir pines en el componente                                         | 3 |

| A.13.Añadir pines en el componente                                         | 3 |

| A.14.Diseño final del componente                                           | ) |

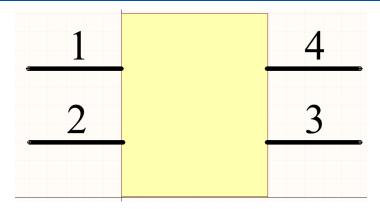

| A.15.Propiedades para los archivos PCB de las librerias                    | ) |

| A.16.Añadir componente para diseño PCB                                     | ) |

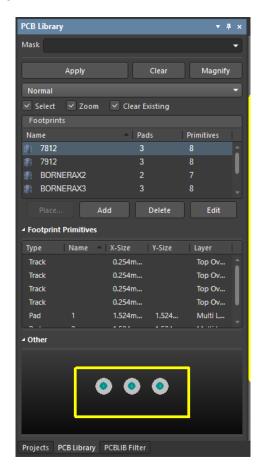

| A.17.Añadir pin al componente                                              | ) |

| A.18.Propiedades de los pines para el componente                           | l |

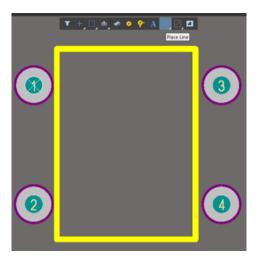

| A.19.Diseño del contorno del componente para la PCB                        | l |

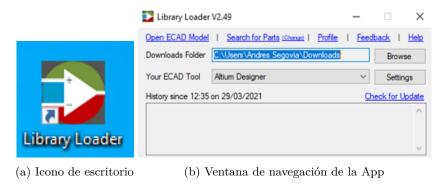

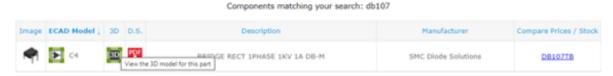

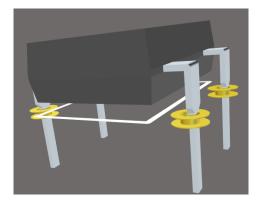

| A.20. Aplicación para obtener modelos en 3D                                | 2 |

| A.21.Modelo 3D del puente rectificador                                     | 2 |

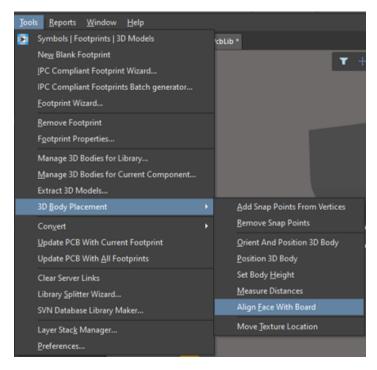

| A.22.Agregar modelo 3D al footprint del componente                         | 2 |

| A.23.Propiedades del modelo 3D                                             | 3 |

| A.24.Modelo 3D añadido al componente                                       | 3 |

| A.25.Modelo 3D del componente                                              | 3 |

| A.26.Alinear modelo 3D con la placa                                        | 1 |

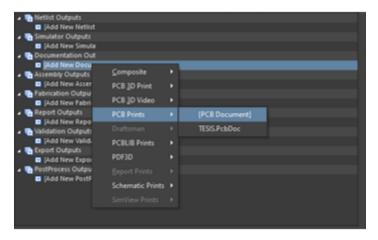

| A.27.Crear archivo de salida en el proyecto                                | ó |

| A.28.Crear un archivo de salida PCB                                        | ó |

| A.29.Alinear modelo 3D con la placa                                        | 3 |

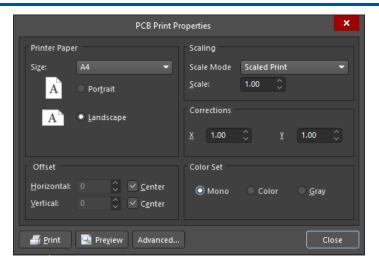

| A.30.Configuración de propiedades del archivo de salida                    | 3 |

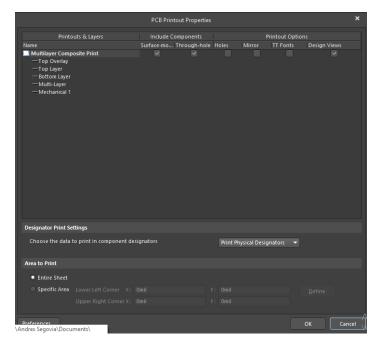

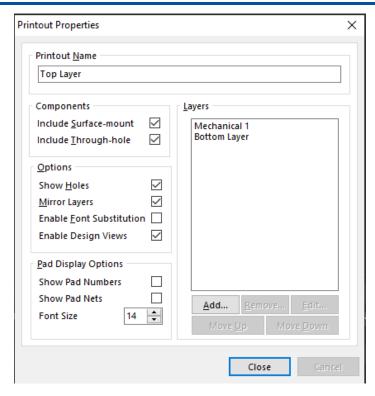

| A.31.Configuración de las capas a imprimir                                 | 7 |

| A.32.Configuración para la generación del archivo PDF                      | 7 |

| A.33.Crear archivo para la salida .gerber                                  |   |

| A.34.Configuración del archivo de salida .gerber                           |   |

| A.35.Creación del archivo para los agujeros                                |   |

| A.36.Configuración de las propiedades para los agujeros                    |   |

| A.37.Generar archivos en el contenedor                                     |   |

| A.38.Archivos generados                                                    |   |

|                                                                            |   |

| A.39.<br>Diseño del PCB de la fuente de alimentación $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$                 | 100 |

|---------------------------------------------------------------------------------------------------------------------|-----|

| A.40.<br>Modelo 3D de la fuente de alimentación $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$             | 100 |

| A.41. Archivo final para impresión de la fuente de alimentación                                                     | 100 |

| A.42.<br>Fuente simétrica de 12V y regulable de 0-5VDC                                                              | 101 |

| A.43.<br>Diseño de la PCB del circuito de acoplamiento $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$               | 101 |

| A.44.Modelado 3D del circuito de acoplamiento                                                                       | 102 |

| $\rm A.45. Circuito$ de acoplamiento de la señal, para lectura de los puertos analógicos del $\overline{\rm DSP}$ . | 102 |

| $\rm A.46.Circuito$ de acoplamiento de la señal, para lectura de los puertos analógicos del $\overline{\rm DSP}$ .  | 103 |

|                                                                                                                     |     |

| B.1. Interfaz de usuario de CCS                                                                                     | 105 |

| B.2. Procedimiento para importar proyecto                                                                           | 105 |

| B.3. Ventana que permite seleccionar el archivo del proyecto a importar                                             | 106 |

| B.4. Ventana que permite seleccionar el compilador para el proyecto                                                 | 107 |

| B.5. Archivo importado correctamente                                                                                | 107 |

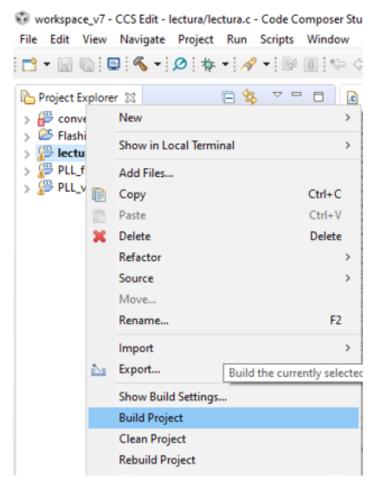

| B.6. Construcción del proyecto                                                                                      | 108 |

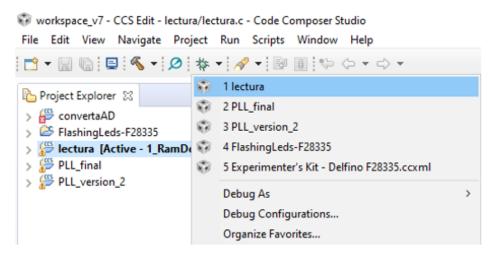

| B.7. Depuración del proyecto para la grabación del código en la tarjeta                                             | 108 |

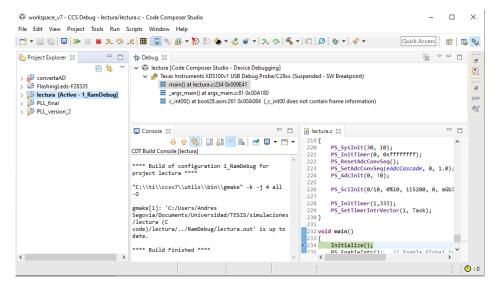

| B.8. Programa en tiempo real                                                                                        | 109 |

# Índice de tablas

| 2.1. | Producción total de energía por fuentes Bioenergéticas                                       | 26 |

|------|----------------------------------------------------------------------------------------------|----|

| 2.2. | Niveles de Voltajes                                                                          | 29 |

| 2.3. | Limites Máximos de Armónicos de Voltaje                                                      | 30 |

| 2.4. | Tiempo de respuesta para frecuencias anormales                                               | 30 |

| 2.5. | Correspondencias utilizadas para la transformación al dominio z $\ \ldots \ \ldots \ \ldots$ | 34 |

| 3.1. | Materiales para el diseño e implementación de la fuente simétrica                            | 45 |

| 3.2. | Valores nominales del partidor de tensión                                                    | 46 |

| 3.3. | Materiales para el diseño del circuito de acoplamiento                                       | 47 |

| 3.4. | Parámetros para el controlador PI utilizados en el sistema                                   | 57 |

| 4.1. | Parámetros y resultados de los algoritmos analizados                                         | 79 |

# Cláusula de Propiedad Intelectual

Yo, Andrés Antonio Segovia Vásquez, autor del trabajo de titulación "Implementación y análisis de algoritmos de sincronización de fase, para fuentes de energía renovables en sistemas trifásicos", certifico que todas las ideas, opiniones y contenidos expuestos en la presente investigación son de exclusiva responsabilidad de su autor.

Cuenca, 26 de julio de 2021

Andrés Antonio Segovia Vásquez

110449514-6

# Cláusula de licencia y autorización para publicación en el Repositorio Institucional

Yo, Andrés Antonio Segovia Vásquez en calidad de autor y titular de los derechos morales y patrimoniales del trabajo de titulación "Implementación y análisis de algoritmos de sincronización de fase, para fuentes de energía renovables en sistemas trifásicos", de conformidad con el Art. 114 del CÓDIGO ORGÁNICO DE LA ECONOMÍA SOCIAL DE LOS CONOCIMIENTOS, CREATIVIDAD E INNOVACIÓN reconozco a favor de la Universidad de Cuenca una licencia gratuita, intransferible y no exclusiva para el uso no comercial de la obra, con fines estrictamente académicos. Asimismo, autorizo a la Universidad de Cuenca para que realice la publicación de este trabajo de titulación en el repositorio institucional, de conformidad a lo dispuesto en el Art. 144 de la Ley Orgánica de Educación Superior.

Cuenca, 26 de julio de 2021

Andrés Antonio Segovia Vásquez

110449514-6

# Certifico

Que el presente proyecto de tesis: Implementación y análisis de algoritmos de sincronización de fase, para fuentes de energía renovables en sistemas trifásicos, fue dirigido y revisado por mi persona.

Ing. Luis Gerardo González Morales, PhD Director

# **Dedicatoria**

## A mi familia y amigos

Este trabajo de titulación, dedico en especial a mis padres que me han apoyado a lo largo de mi formación académica, por su incondicional amor, a mis hermanas y mi sobrina que han estado conmigo, a mis amigos que sin duda me han apoyado.

Andrés Segovia

# **Agradecimientos**

En primer lugar extiendo mi agradecimiento al Ingeniero Luis González que me ha brindado sus conocimientos y su apoyo como guía a lo largo de este trabajo de titulación, así como tu total confianza para alcanzar los objetivos del presente trabajo.

También extiendo un agradecimiento a Pablo Delgado y al Ing. Edisson Villa encargados del Laboratorio del Micro Red, que me han dado un espacio de trabajo amigable y lleno de conocimientos, a pesar de las restricciones establecidas me han dado su confianza para poder realizar las pruebas en el Laboratorio, sin su ayuda no hubiera sido posible este trabajo.

Andrés Segovia

# Abreviaciones y Acrónimos

```

ARCONEL Agencia de Regulación y Control de Electricidad. 29

AT alta Tensión. 26, 27

BT baja Tensión. 28

CCS Code Composer Studio. 1, 2, 4, 6, 7, 10, 20, 22, 41, 43, 49, 50, 80, 104, 105

DDSRF-PLL Decoupled Double Synchronous Reference Frame-Phase Locked Loop. 7, 19, 36, 38,

39, 78-80

DR recursos distribuidos. 30

DSOGI-PLL Dual Second-Order Generalized Integrator-Phase Locked Loop. 19, 78–80

DSP Digital Signal Processor. 1, 2, 8, 10, 20, 22, 26, 41–43, 48–50, 53, 68, 69, 75, 79, 80, 102, 103

DSRF-PLL Decoupled Stationary Reference Frame-Phase Locked Loop. 19

GNL Gas Natural Licuado. 18, 19

GSC Grid Size Converters. 26

HD Total Harmonic Distortion. 29

IDE Integrated Development Environment. 41

IRENA International Renewable Energy Agency. 24

MT media Tensión. 26, 27

PCB Printed Circuit Board. 44, 82–84, 87, 90, 91

PCC punto de acoplamiento en común. 19, 26, 28-31

PI Proporcional-Integral. 5, 32, 35, 36, 56

PLL Phase-Locked Loop. 19, 31–33

PSE Positive Sequence Extractor. 40

RES Renewable Energy Sources. 2, 18, 19, 22, 26, 29, 32, 71, 76, 78, 81

SCI Serial Communication Interface. 4, 7, 42, 47, 49, 50, 52, 53, 56, 69, 110

SISO Single Input Single Output. 33

SNT Sistema Nacional de Transmisión. 22

SRF-PLL Synchronous Reference Frame-Phase Locked Loop. 19, 39

TI Texas Instruments. 41

VCO Voltage Controlled Oscillator. 19, 31, 32, 34

```

CAPÍTULO

# Introducción

En este capítulo se contextualiza la problemática de la interconexión entre las Renewable Energy Sources (RES) y la red eléctrica pública, sus limitantes y ventajas. Es así, que en la sección 1.1 se presenta la introducción, en la que se habla de la problemática y se establecen pautas de la solución de este trabajo, en la sección 1.2 se presentan los antecedentes, a continuación, se presentan los alcances del proyecto en la sección 1.3, posteriormente se establecen los objetivos en la sección 1.4 y finalmente se presenta la estructura del documento en la sección 1.5.

## 1.1. Introducción

En la actualidad, el desarrollo tecnológico ha permitido que poco a poco el Gas Natural Licuado (GNL), utilizado como combustible para la generación de energía eléctrica, sea reemplazado por fuentes de energía renovables alternativas (RES), que sean confiables y seguras, estas fuentes de energía limpias, tales como, solar, eólica o hidráulica; tienen la posibilidad de inyectar su energía eléctrica generada a la red pública, en el nivel de transmisión o en el de distribución, esto depende de la capacidad de generación de cada fuente.

Para lograr inyectar la energía generada, es necesario que las redes cumplan ciertos parámetros técnicos que permiten que la red sea eficiente y no cause daños en los equipos terminales o en los inversores de las centrales de la red principal. Es por ello que en cada región, se establecen códigos que permiten evitar estos problemas, entre ellos se establece parámetros como redes sincronizadas en fase, frecuencia de la red, la regulación del voltaje, el número de armónicos, reconexión ante fallas, etc.

Uno de los parámetros más importantes a considerar es la sincronización entre generadores, para lograr este objetivo se han desarrollado diferentes metodologías, tales como, algoritmos matemáticos que van de la mano con sistemas de electrónica de potencia y sistemas de control, que permiten lograr este objetivo. Entre ellos se encuentran la detección de cruce por cero, este procedimiento se basa en detectar cuando la amplitud de la señal cambia de positivo a negativo o viceversa, es decir cuando la señal cruza por el eje del tiempo (eje x).

Este procedimiento resulta ser el más sencillo, pero a su vez ineficiente, esto debido a que la señal

no es completamente pura, es decir no es perfectamente senoidal, por lo que conlleva a que exista armónicos en la señal de entrada. Estas distorsiones en la señal se pueden interpretar como un cruce por cero de la señal original, impidiendo la correcta sincronización del sistema.

Por el contrario, existen otros métodos de control que son los **Lazo de bloqueo de fase** (Phase-Locked Loop (PLL)), su funcionamiento se centra en detectar la fase de la señal de entrada, luego ingresa al filtro de primer orden o al controlador PI, que permite obtener la fase, a partir de una frecuencia de referencia, finalmente esta fase, pasa al **Oscilador Controlado por Voltaje** (Voltage Controlled Oscillator (VCO)), para generar la señal de salida.

Con estos antecedentes, a lo largo del tiempo se han ido desarrollando algoritmos de acuerdo con la calidad de la red de cada región, esto ha permitido mejorar los PLLs, para lograr mayor eficiencia en la sincronización, permitiendo así una mejor distribución de las RES, logrando un amplio desarrollo energético a lo largo de la región.

# 1.2. Antecedentes

Debido a la fuerte demanda energética a nivel mundial y al proceso de innovación en la generación de energía limpia, con la finalidad de reemplazar los generadores de energía con GNL, en el Ecuador se han experimentado nuevas fuentes de energías renovables, como son la hidráulica (COCA CODO SINCLAIR) y eólica (Villonaco-Loja), estos proyectos permiten un gran avance en generación de energía limpia, produciendo grandes cantidades de energía al mes.

A su vez, nuevos proyectos se empiezan a desarrollar, como la construcción de parques solares, que producen energía mediante paneles solares, con ello a lo largo del país existen empresas que han optado por tener su propio parque solar instalado en sus edificios, esto a gran escala. Por otro lado, debido a que su precio ha disminuido en los últimos años, actualmente se pueden adquirir para su uso doméstico. Estas fuentes, se deben interconectar a la red pública, en un punto de acoplamiento en común (PCC).

Al tener dos fuentes de energía distinta, existe problemas de sincronización, causando daños en la línea principal, consecuentemente se dan penalizaciones para los usuarios que instalan estos generadores. Para evitar esto, se utilizan sistemas de control como los PLLs y sus variantes, dichos algoritmos han ido evolucionando dependiendo a la calidad de energía de la red principal, por lo que se han implementado variantes como PLL con marco de referencia síncrono (Synchronous Reference Frame-Phase Locked Loop (SRF-PLL)), PLL con desacople en el marco de referencia estacionario-PLL (Decoupled Stationary Reference Frame-Phase Locked Loop (DSRF-PLL)), PLL con doble integrador generalizado de segundo orden (Dual Second-Order Generalized Integrator-Phase Locked Loop (DSOGI-PLL)), PLL con doble desacople en el marco de referencia síncrono-PLL (DDSRF-PLL), etc.

Estos algoritmos de control, tienen como idea principal, entregar una buena calidad de energía a la red, además, poder contribuir con el medio ambiente ya que provienen de RES, con ello se puede asegurar que los equipos conectados a su red, puedan trabajar sin problemas.

#### 1.3. Alcance

En el desarrollo de este trabajo, se implementan los algoritmos de sincronización como: SRF-PLL, DSRF-PLL, DSOGI-PLL, DDSRF-PLL; utilizando herramientas computacionales como el PSIM® y

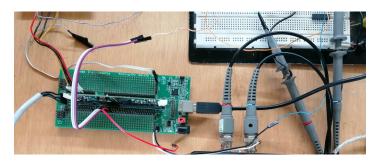

CCS, además se utiliza un DSP TMDSCNCD28335 para poder almacenar dichos algoritmos. El DSP se encargará de realizar la adquisición de datos, es decir, este dispositivo por medio de las entradas analógicas, captura la señal de entrada, luego por medio del modulo A/D, permite digitalizar la señal, para finalmente realizar el procesamiento de la misma, con los algoritmos mencionados.

Por lo tanto, para la adquisición de datos, se necesita que la señal de entrada, esté acorde a las especificaciones técnicas de las entradas analógicas, por lo que se implementará un circuito de acondicionamiento de la señal que permite el correcto acoplamiento.

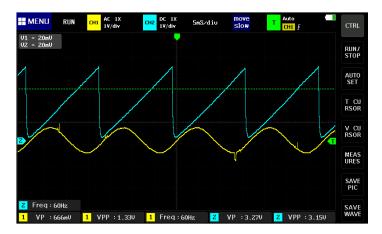

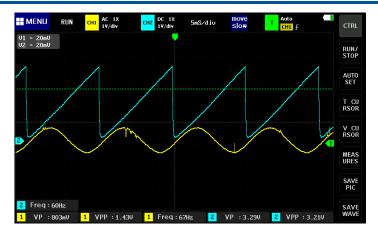

Para visualizar el comportamiento de cada algoritmo, se utiliza el osciloscopio del software PSIM, para ello se realiza la comunicación serial entre el DSP y la PC por medio de un convertidor USB-Serial.

# 1.4. Objetivos

## 1.4.1. Objetivo general

Implementación y estudio de algoritmos de sincronización para sistemas trifásicos, en la red del laboratorio de Micro Red de la Universidad de Cuenca.

## 1.4.2. Objetivos específicos

El presente trabajo tiene los siguientes objetivos específicos:

- Estudio del estado del arte para comprender el funcionamiento de cada algoritmo.

- Implementación de los algoritmos estudiados en las plataformas de PSIM y CCS

- Diseño y construcción de los circuitos de acondicionamiento entre la red y el DSP

- Implementación del proceso de comunicación entre la PC y DSP

- Análisis del comportamiento obtenido con cada algoritmo.

## 1.5. Estructura del documento

En este capítulo se ha priorizado la importancia de los algoritmos de sincronización de fase para el uso de fuentes de energías limpias como reemplazo de los derivados de petróleo, además que permite que los ciudadanos puedan ser generadores de su propia energía y aportar a la red principal sin causar daños en la misma, posteriormente el documento se encuentra estructurado de la siguiente manera:

- Capítulo 2: presenta una revisión de los principales generadores eléctricos renovables y no renovables, luego se da a conocer la estructura y los aspectos regulatorios, de los sistemas de transmisión y distribución eléctricos. También se da a conocer los fundamentos teóricos de los elementos que integran el sistema de control de cada algoritmo de sincronización, en conjunto con su estructura. Finalmente se presenta la descripción técnica y teórica de los componentes de software y hardware que se utilizan en el desarrollo del trabajo de titulación.

- Capítulo 3: presenta de forma esquemática el diseño y la implementación de los algoritmos de sincronización utilizados para el estudio, además se detalla los sistemas de control y electrónica de potencia que se han utilizado para el funcionamiento del sistema.

• Capítulo 4: se presenta los datos técnicos de los escenarios en los que los distintos algoritmos fueron probados, se expone los resultados obtenido en la puesta en marcha del sistema, realizando un análisis comparativo del rendimiento de cada algoritmo. Finalmente se presenta las contribuciones y experiencias tratadas en el trabajo de titulación, introduciendo trabajos futuros en base a la temática tratada.

2 Pituro

# Marco Teórico

En este capítulo se presenta el sustento teórico en la que se fundamenta la propuesta de este trabajo de titulación. Este capítulo inicialmente presenta una reseña global de los distintos generadores de fuentes de energías en la sección 2.1, luego se realiza un enfoque de la estructura técnica de los sistemas de transmisión y distribución eléctricos en la sección 2.2. Además se introduce una explicación de los aspectos regulatorios del Sistema Nacional de Transmisión (SNT) en la sección 2.3. Posteriormente en la sección 2.4 se realiza una explicación de los algoritmos existentes en el campo de la sincronización. Asimismo en la sección 2.5 se detalla los aspectos del software PSIM, luego se explica sobre los aspectos técnicos del DSP en la sección 2.6 y finalmente en la sección 2.7 se explica sobre el software CCS.

# 2.1. Fuentes de Generación de Energía Eléctrica Renovables y No Renovables

Las fuentes de energía a nivel mundial, son recursos de primera necesidad, debido a su vital importancia, ya que permiten la generación de energía eléctrica, para el consumo humano.

Con esto se presentan ciertos problemas, ya que se requiere que su fuente de energía vaya acorde a las posibilidades de cada región, por ejemplo en Ecuador, el caudal de las fuentes hídricas son significativas, por lo que su principal fuente de energía es la hidráulica, permitiendo así, que este sea exportador de energía.

Sin embargo, en otras regiones su principal fuente de energía proviene del petróleo o sus derivados, lo que conlleva a buscar nuevas formas de energía alternativa, aun así teniendo en cuenta que cada año el desarrollo de las RES va incrementando, las fuentes no renovables tiene un porcentaje alto en generación de energía, llegando a tener un 73 % de participación en el mercado, frente al 27 % que proviene de fuentes renovables como hidráulica, solar y eólica. [1]

#### 2.1.1. Fuentes de Generación de Energía no renovables

Los generadores de energía no renovables, son aquellos que han sido de uso común, entre ellas están aquellas que funcionan con derivados de petróleo, estas fuentes resultan ser más prácticas ya que se tiene la posibilidad de transportar la materia prima hasta las estaciones principales, para posteriormente someterlas a un proceso para generar energía. Al ser no renovables, estas fuentes causan un gran impacto al medio ambiente, por lo que se han desarrollado estudios en varias regiones para poder disminuir el uso de estas fuentes o a su vez desarrollar métodos para no causar graves impactos ambientales. [2]

#### 2.1.1.1. Petróleo

El petróleo es la principal fuente de energía a nivel mundial, abarcando aproximadamente el 31 % de la producción total de energía [1]. En el año 2019 se generó aproximadamente 8000TWh. Este producto se obtiene de restos fósiles, formado de varios gases, principalmente de azufre [3]. El crudo, como se lo conoce habitualmente, en los últimos años ha tenido una caída exponencial en el precio del barril, esto debido a la saturación del mercado y la falta de demanda [4].

Este problema ha llevado a que la economía mundial esté en riesgo ya que es uno de los principales productos de comercio a nivel mundial y su gran impacto en el tema energético resulta ser de gran relevancia, por ser su principal fuente de energía [5], además que sus derivados resultan ser esenciales para el consumo en la vida cotidiana, como la gasolina, el diésel, el gas, kerosene, etc.

#### 2.1.1.2. Carbón

EL carbón es un mineral, considerado como la primera fuente de energía, este mineral abarca aproximadamente un 26 % de producción de energía a nivel mundial [1]. Al inicio de la revolución industrial, el carbón fue la principal fuente de generación de energía, [3][6], por consiguiente, era el principal elemento para poner en marcha a los motores de los principales medios de transporte e incluso motores de las industrias en donde se trabajaba con hierro y acero.

En el año 2019, a nivel mundial se generó aproximadamente **7000TWh**. Este mineral es un recurso abundante sobre la tierra por lo que es la principal fuente de energía a nivel industrial, países como Estados Unidos y China, son los principales consumidores de este mineral [3].

#### 2.1.1.3. Gas Natural

El gas natural se encuentran en los yacimientos fósiles, estos se pueden encontrar con o sin fuentes de petróleo y son procesados para su uso comercial. En la industria, el gas natural permite generar energía térmica, es decir son más utilizados en la industria metalúrgica [7]. Este producto también es de uso doméstico, por lo que, conlleva grandes ventajas con respecto a otros derivados de petróleo que se trataron anteriormente.

Entre las ventajas más importantes, no emite grandes cantidades de C02, por lo que en ciertas regiones de Europa como en España, se ha impulsado el reemplazo del carbón por el gas natural como fuente de respaldo. [8] A nivel mundial, el gas natural abarca el 23 % de la generación de energía eléctrica, produciendo aproximadamente **6000TWh** en el año 2019.

#### 2.1.1.4. Nuclear

La energía nuclear es aquella energía contenida en el núcleo de los átomos, que al ser estimulados, liberan su energía contenida, esto produce que se genere energía calorífica, lo que a su vez produce vapor, esto entra a las turbina que son las encargadas de producir energía eléctrica. En China [5], la energía nuclear es la principal fuente encargada de reemplazar las fuentes de carbón, ya que emite CO2 en pequeñas cantidades.

Este tipo de energía se puede obtener de dos procesos diferentes que son: la fisión, que consiste en partir el núcleo del átomo y la fusión que une el núcleo del átomo; estos procesos por lo general se logran usando Uranio o Plutonio [9], por su inestabilidad, no se encuentran fácilmente en la naturaleza, estos pueden generar un ambiente radiactivo permanente por años.

En el 2018, a nivel mundial, se tuvo 450 reactores operativos, por lo que la capacidad energética producida a nivel mundial fue de **2563TWh** [10] [11]. En el 2019 la capacidad obtenida fue de **2657TWh** aproximadamente.[12]

## 2.1.2. Fuentes de Generación de Energía Renovables

Las fuentes de energía renovables, son aquellas que se obtienen de fuentes limpias e inagotables, además no emiten CO2. Debido al impacto ambiental actual, los gobiernos se han visto obligados a desarrollar a gran rapidez estas fuentes de energía.

Existen muchos países que se encuentran migrando sus fuentes de energía contaminantes a energías limpias, por lo que en el 2009, se creó International Renewable Energy Agency (IRENA), una institución que permite la cooperación internacional de políticas, recursos, tecnología, etc, permitiendo así que más países se unan a estos proyectos. IRENA actualmente cuenta con 180 países adscritos a este proyecto de transformación.

## 2.1.2.1. Hidráulica

La fuente de energía hidráulica produce energía en base a la fuerza y el movimiento del agua, por lo general se utilizan ríos o vertientes de la montañas, que permiten mover las turbinas.

Una de las grandes ventajas de estas fuentes es que posee una gran nivel de respuesta inmediata ante fluctuaciones, lo que permite cubrir picos de demanda de manera confiable. En el 2019 se generó cerca del 16.2% de energía eléctrica a nivel mundial [1]. Estas estadísticas apuntan a que el crecimiento de producción de energía en las hidroeléctricas vaya en aumento.

El crecimiento hasta el 2018 ha sido cerca de **4000TWh**, por lo que se pretende que cada año vaya incrementando. [13]. Entre los países que cuentan con las hidroeléctricas más grandes del mundo están: China, Brasil, Estados Unidos y Rusia. Estos países, en conjunto con más de 160 países [14], están llevando a las hidroeléctricas a ser las primeras fuentes de energía en el mundo, ya que se ha observado que cada año la capacidad de producción por país es mayor.

#### 2.1.2.2. Eólica

Las fuentes de energía eólica son aquellas que utilizan la velocidad del viento para mover la turbina que permite generar energía, es decir, utiliza la energía cinética creada por el movimiento del aire. En los últimos años, la presencia de este tipo de fuente ha ido creciendo, teniendo un 6% de energía generada en relación a las fuentes de energía renovables. [1]

En el año 2018 las fuentes eólicas generaron alrededor de 1200 TWh a nivel mundial, la capacidad de generación ha crecido en los últimos años. En el 2019 la energía hidráulica experimentó el crecimiento del 1.1 % [1], al punto que, la generación de energía con derivados de petróleo o carbón, ha caído, por lo que se pretende incrementar el número de turbinas instaladas en el mar, para llegar en los próximos años, reemplazar las fuentes de energía no renovables.

La energía eólica es la segunda fuente de energía renovable con más capacidad de generación en el mundo, después de la hidráulica. [3]

#### 2.1.2.3. Solar

La energía solar es la energía más abundante en la tierra que se puede obtener de dos formas: fotovoltaica y térmica. Se estima que la energía que proviene del sol está entre los **1.5x10**<sup>11</sup> y **1.8x10**<sup>11</sup> **MW**. [3] En el 2019 esta fuente generó aproximadamente el 3% de lo generado por todas las energías renovables en el mundo. [1]

Sin embargo, la producción se divide en dos, siendo la fotovoltaica la principal fuente de generación eléctrica solar. Las fuentes fotovoltaica se basan en el efecto fotoeléctrico, estas fuentes utilizan un material semiconductor que puede ser de silicio mono-cristalino, poli-cristalino o amorfo, estos materiales absorben los fotones y liberan electrones, generando flujos de corriente en las celdas [13]. Este proceso generó aproximadamente 550TWh alrededor del mundo en el año 2018.

Por otro lado las fuentes concentradas, absorbe los rayos de sol utilizando espejos, lo que permite calentar el fluido generando vapor y moviendo las turbinas; en relación con las fotovoltaicas se puede seguir generando energía aun sin la presencia del sol, pues almacena vapor que puede ser reutilizado [13], este proceso generó 12.200GWh de energía en el año 2018 a nivel mundial.

#### 2.1.2.4. Biomasa

La biomasa permite aprovechar los desechos orgánicos: sólidos (leña, astillas, carbón vegetal, etc.), líquidos (alcoholes, hidrocarburos, aceites vegetales, etc.) o gaseosos (gas de gasógeno, biogas, hidrógeno). Este tipo de generación energético se ha desarrollado con gran rapidez en los últimos años, permitiendo a países como España, Estados Unidos, China o Brasil, reemplazar los combustibles fósiles a escala industrial, debido a que en algunas fábricas las instalaciones de calderas gigantes es un hecho, esto les permite quemar materiales de sus propios desechos de materia prima o de material de fabricación. Entre los principales materiales que se utilizan para la generación de energía se tiene a la madera, que a lo largo de los tiempos el hombre ha utilizado para generar calor. [15]

En contexto energético, las tres cuartas partes del porcentaje total de la generación de energía con fuentes renovables, abarca la bioenergía [16], considerando que más de la mitad consiste en el uso de materiales tradicionales de biomasa. La bioenergía representó aproximadamente el  $10\,\%$  del consumo

total de energía final y el 1,9 % de la generación de energía mundial en 2015. [13]

En el 2019 la producción de bioenergía a nivel mundial, abarcó el 9 % de a energía total [1], en la tabla 2.1 se presentan las principales fuentes de generación con su respectiva capacidad energética producida, con ello que se prevé que en los próximos años, estas fuentes de energía reemplacen a nivel industrial a los combustibles fósiles. Con estos resultados, se ha visto reflejado el compromiso de ciertos organismos estatales por el desarrollo energético y el medio ambiente.

| Fuente Bioenergéticas | Energía producida (GWh) |

|-----------------------|-------------------------|

| Biocombustible íquido | 7.344                   |

| Desechos municipales  | 62.148                  |

| Biogas                | 88.378                  |

| Biocombustible sólido | 365.034                 |

Tabla 2.1: Producción total de energía por fuentes Bioenergéticas

# 2.2. Estructura de los Sistemas de Transmisión y Distribución Eléctricos

En el apartado anterior se habló de las fuentes de energía renovables y no renovables, que resultan ser la parte principal de un sistema eléctrico. Estas fuentes se encuentran principalmente en las centrales eléctricas.

Considerando que, para la transmisión y distribución, las fuentes de energía externas se interconectan a la red principal, en un PCC, en este punto se realizan controles de acuerdo a los códigos de cada región, además que se realizan métodos de sincronización para poder realizar esta operación.

Es por ello que cada RES necesita su convertidor basado en electrónica de potencia (Grid Size Converters (GSC)), estos elementos deben funcionar en condiciones normales y anormales, es decir deben ser robustos, capaces de actuar ante fallas críticas de la red.[17][18][19]

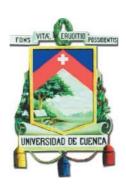

Como se observa en la figura 2.1 se tiene un sistema de control de sincronización de fase, utilizando DSP que permite realizar el procesamiento de la señal, para conectar una red principal con una fuente de energía externa.

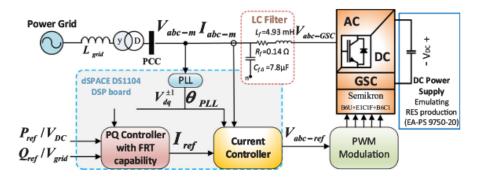

A más de las fuentes generadoras, como se puede ver en la figura 2.2, un sistema eléctrico consta también de elementos, materiales e instalaciones que permiten transmitir y distribuir energía eléctrica desde las plantas principales pasando por subestaciones y terminando en los usuarios finales ya sean domésticos o industriales.

La **red de transporte** es la encargada de conectar las estaciones elevadoras con las subestaciones reductoras, esta se puede dividir en dos partes que son: redes de transporte de alta Tensión (AT) y redes de transporte de media Tensión (MT). La función principal de las redes de AT es transportar energía a grandes distancias, por lo que es importante elevar la tensión en las centrales elevadoras para que exista la menor cantidad de pérdidas en la línea (por lo general se eleva la tensión a voltajes aproximados a 138kV, 230kV, 500kV o mayores [21]). Es importante saber que también pueden existir

Figura 2.1: Topología básica de conexión de fuentes renovables con la red principal [17]

Figura 2.2: Esquema de una sistema de Generación, Transmisión y Distribución de la red Eléctrica. [20]

redes de distribución de AT y MT.[22]

Los principales elementos que conforman las redes de transmisión son:

- Torres de transmisión: es una estructura que permite colocar las lineas de transmisión. Comúnmente son torres de 25 o 45m de altura, dependiendo de la cantidad de circuitos que vayan sobre la torre, debiendo considerar la franja de servidumbre. [23]

- Líneas de transmisión: son los conductos por donde se va a transportar la energía, estos conductos se seleccionan debido a su capacidad a transportar, caída de tensión y pérdidas de potencia, etc.

- Aisladores de línea: Son los encargados de sujetar mecánicamente a los conductores, estos se encuentran aislados por lo que no permite conducción eléctrica en las sujeciones de la torre.

- Subestaciones: Las subestaciones, son pequeños sectores en donde se establece el voltaje necesario para su transmisión, estas son encargadas de elevar o disminuir la tensión según lo requiera la zona a transportar.

- Compensación de potencia reactiva: permite regular los voltajes de las barras de transmisión, estos se encuentran en las subestaciones, en donde hallamos bancos de inductores o capacitores. [24]

- Transformadores: Estos elementos son los encargados de elevar o disminuir la tensión en las

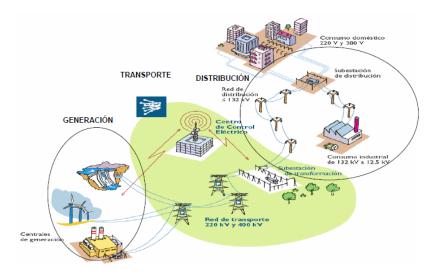

Figura 2.3: Estructura general de un Sistema Eléctrico  $\left[ 20\right]$

subestaciones o en los centros de generación, estos elementos deben ser fijados de acuerdo a la cargabilidad que soportará cada uno según las normativas de cada región. [24]

En relación a la **red de distribución**, son redes de baja Tensión (BT) que son utilizadas para la comercialización, tanto doméstica como industrial. Estas redes pueden estar de forma aérea o subterránea. Uno de los componentes importantes son los centros de transformación, que son los encargados de regular el voltaje que llega de las subestaciones para el consumo doméstico o industrial. De forma general en la figura 2.3 se presenta un esquema general del sistema eléctrico (como se observa, tiene relación con lo mencionado anteriormente).

# 2.3. Aspectos Regulatorios para la Transmisión y Distribución de Energía Eléctrica

Uno de los aspectos más importantes para la conexión entre distintas fuentes de energía son las regulaciones técnicas que se establecen en cada región. Esto permite que una fuente externa no cause perturbaciones en la red eléctrica principal, con el fin de evitar problemas en los equipos de consumo o en las plantas generadoras principales.

Varias fuentes de energía renovables y no renovables, pueden estar conectadas en un PCC, esto permite que las fuentes, dependiendo de su capacidad generadora, pueden conectarse a una red de transmisión o distribución. Con ello, debido al desarrollo tecnológico, se ha logrado diseñar e implementar fuentes de energía de uso comercial como paneles fotovoltaicos, que pueden instalarse de forma

rápida y correcta en los domicilios.

Estas fuentes comerciales tienen la capacidad de disminuir el consumo eléctrico de la red principal o a su ves entregar a la red carga residual que no es aprovechada por el consumidor, esto permite al usuario vender parte de su energía generada al distribuidor de energía la región.

A continuación, se describe los aspectos técnicos más relevantes que se consideran para la interconexión de fuentes externas con la red principal, para esto se ha tomando en consideración el estándar IEEE Interconnecting Distributed Resources with Electric Power Systems [25], que permite conectar diferentes RES, en un PCC, también se han tomando en cuenta las recomendaciones de la serie 1547 Para la Interconexión Recursos energéticos distribuidos [26], [27], [28]. Además el estándar IEEE Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces [29], otorga ciertas normas que permite interconectar paneles fotovoltaicos a la red. Debido a que cada región tiene sus propios códigos se ha considerado las resoluciones de la Agencia de Regulación y Control de Electricidad (ARCONEL) REGULACIÓN No. 004/15 [30], 005/18 [31], relacionado con los aspectos técnicos y calidad de servicio de la distribución y comercialización de la red eléctrica y la resolución REGULACIÓN Nro. ARCONEL – 003/18 para la Generación fotovoltaica para autoabastecimiento [32].

#### 2.3.1. Nivel de voltaje

Los niveles de voltajes son valores que clasifican las redes de transmisión o distribución, estos valores pueden tener ciertas variaciones que son admitidas por el ente regulador. En la tabla 2.2 se puede observar las características de los niveles de tensión regulados por la ARCONEL.

| Clasificación        | Nivel de voltaje                      | Variación permitido |

|----------------------|---------------------------------------|---------------------|

| Bajo Voltaje         | menor igual a 0,6 kV                  | +- 8.0 %            |

| Medio Voltaje        | mayor a $0.6$ y menor igual a $40$ kV | +- 6.0 %            |

| Alto Voltaje Grupo 1 | mayor a 40 y menor igual a 138 kV     | +- 5.0 %            |

| Alto Voltaje Grupo 2 | mayor a 138 kV                        | +- 5.0 %            |

Tabla 2.2: Niveles de Voltajes

## 2.3.2. Perturbaciones rápidas de voltaje (Flicker)

Estas perturbaciones moderadas de voltaje, son fluctuaciones en la luminosidad, que pueden ser percibidas por el ojo humano.

## 2.3.3. Distorsión armónica de voltaje

Son perturbaciones causadas por las cargas no lineales conectadas a la red, esto causa que la forma de onda de voltaje o corriente se altere, causando daños en los equipos finales o en las plantas distribuidoras. En la tabla 2.3 se presenta los límites permitidos de armónico individual y Total

Harmonic Distortion (HD), establecidos por el ente regulador, en la regulación citada en [31] se presenta las fórmulas para su cálculo.

Tabla 2.3: Limites Máximos de Armónicos de Voltaje

| Nivel de voltaje     | Armónico individual | THD  |

|----------------------|---------------------|------|

| Bajo Voltaje         | 5 %                 | 8.0% |

| medio voltaje        | 3 %                 | 5.0% |

| alto voltaje Grupo 1 | 1.5 %               | 2.5% |

| alto voltaje Grupo 2 | 1 %                 | 1.5% |

## 2.3.4. Desequilibrio de voltaje

El desequilibrio de voltaje se produce cuando cargas monofásicas o bifásicas se conectan de manera desbalanceada a la red trifásica, lo que ocasiona que los equipos resulten afectados.

#### 2.3.5. Frecuencia

Cuando por distorsiones de voltaje sobrepasa los niveles de la tabla 2.4, los recursos distribuidos (DR) se desconectan de la red principal por un instante de tiempo, llamado tiempo de limpieza, en este tiempo los DR ajustan sus parámetros a los establecidos por la red principal. Algunos valores pueden ser ajustados en campo.

Tabla 2.4: Tiempo de respuesta para frecuencias anormales

| Rango DR    | Rango de frecuencia (Hz) | Tiempo de limpieza (s) |

|-------------|--------------------------|------------------------|

| $\leq 30kV$ | >60.5                    | 0.16                   |

|             | < 50.3                   | 0.16                   |

| >30kV       | >60.5                    | 0.16                   |

|             | <59.8-57.0(ajustable)    | 0.16-300 (ajustable)   |

|             | < 57.0                   | 0.16                   |

## 2.3.6. Sincronización

Los DR deben estar en paralelo con los sistemas de potencia del sector, conectados a un PCC sin causar interferencias en la línea mayor a +-5 % del nivel de voltaje establecido en el sistema de potencia.

## 2.3.7. Reconexión al sistema de potencia eléctrico

Cuando existe una falla en el área de sistema de potencia, el DR es desconectado, hasta que el voltaje del sistema se encuentre en los rangos establecidos por cada región, además que cada DR tendrá que tener un retardo ajustable después de la interconexión del sistema de potencia, a la red.

Figura 2.4: Detección de cruce por cero de una señal senoidal ruidosa [35]

# 2.4. Algoritmos de Sincronización de Red

Debido a las perturbaciones que se presentan en la interconexión de fuentes en un PCC, es necesario implementar métodos, capaces de permitir que los parámetros de las fuentes se asemejen entre sí para evitar daños, para ello los algoritmos de sincronización permiten sensar los parámetros de la red principal y por medio de procesamientos de señales adaptar las fuentes externas a los mismo.

# 2.4.1. Detección de cruce por cero

La detección de cruce por cero es uno de los métodos más sencillos, que permite capturar el estado transitorio de la onda senoidal cuando pasa de 0° a 180° en AC. Este tipo de circuito, resultan ser eficientes cuando la señal es más pura, es decir cuando no hay presencia de armónicos o perturbaciones en la señal. En circuitos de corriente alterna, la señal no es completamente pura, ya sea por elementos no lineales conectados a la misma o por el simple hecho de la distribución, por lo que se tiene fluctuaciones en los cambios de amplitud, permitiendo que el algoritmo, realice una detección falsa de cruce por el eje. [33] Debido a estos problemas, se han desarrollado algoritmos con filtros que permitan tener la señal más pura, para tener una mejor percepción de la señal original y hacer que el algoritmo sea más eficiente, como nos indica [34] en donde busca la optimización configurando sistemas analógicos que permitan un correcto sensado.

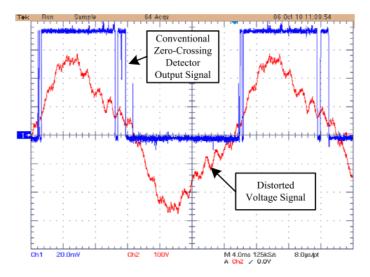

En la figura 2.4 se puede observar que la señal no es pura por lo que, incluso puede tener armónicos no deseados, provocando que la onda tanto en amplitud como en frecuencia se distorsione y que la detección de cruce no sea fiable.

#### 2.4.2. Algoritmos de lazo de bloqueo de fase (PLL)

Otros métodos desarrollados para sincronización de red, son los PLL, estos algoritmos permiten sincronizar la señal, tomando en consideración una señal de entrada (frecuencia y fase). En la figura 2.5 se presenta el diagrama de bloque del funcionamiento general del sistema, se observa que básicamente un PLL esta conformado por un detector de fase, un filtro de lazo y un VCO. [36] [37] [38] [39]

Figura 2.5: Diagrama de Bloques básico de un PLL

Debido a que en cada región la calidad de la red eléctrica es variable, se han desarrollado diferentes cambios en la estructura principal de los PLL con ello se ha logrado tener mejor rendimiento en la sincronización de fase.

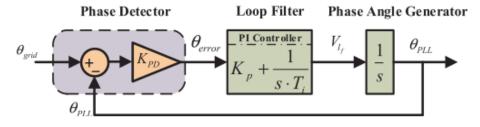

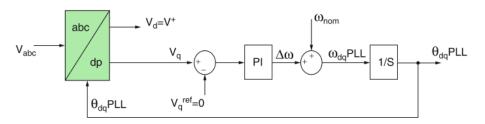

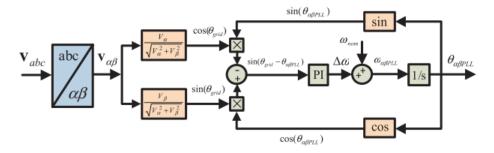

De forma analítica los PLL se pueden conformar como se presenta en la figura 2.6, observando que es necesario trabajar con la fase de la RES, para poder sincronizar con la red principal. En este contexto inicialmente se realiza una detección de fase, esto se logra comparando la fase de la señal de entrada ( $\theta_{grid}$ ) con la señal generada ( $\theta_{PLL}$ ) por el VCO, obteniendo una señal de error ( $\theta_{error}$ ) con distorsiones de frecuencias altas, por lo que luego, se introduce un filtro de lazo para eliminarlas, a esta señal filtrada se introduce una frecuencia de referencia ( $\mathbf{W}_{ref}$ ), obteniendo una señal  $V1_f$ , que finalmente ingresa al VCO para obtener la fase de la señal  $\theta_{PLL}$ , para ello se tiene en cuenta la ecuación 2.1.

$$\theta = \int \omega(t)dt \tag{2.1}$$

Figura 2.6: Topología básica de los PLL ([17])

El aspecto más importante en los esquemas **PLL** es el controlador **PI**, por lo que se debe calcular los parámetros para sintonizar el mismo. Sabiendo que las funciones de transferencia deben estar en el dominio discreto, se puede encontrar la función de transferencia en el dominio continuo y utilizando correspondencias entre la transformada de Laplace y transformada Z, se realiza la transformación para la modelización en el dominio discreto.

Utilizando el esquema mencionado en la figura 2.6 de la sección 2.4.2, se tiene la función de transferencia de lazo abierto  $(F_{OL}(s))$  como se observa en la ecuación 2.2, para ello se considera una ganancia para el detector de fase  $k_{pd} = 1$ , ya que las distorsiones de frecuencia baja pueden aumentar

su amplitud y causar problemas en el bucle de control.

Siendo PDs la función de transferencia del **detector de fase**, LFs la función de transferencia del Filtro de Lazo, VCOs la función de transferencia del VCO. En donde  $K_p$  es la constante proporcional y  $T_i$  representa el tiempo integral.

$$F_{OL}(s) = PD(s) * LF(s) * VCO(s)$$

$$= k_{pd} * (k_p * (1 + \frac{1}{s * T_i})) * \frac{1}{s}$$

$$= \frac{k_p s + \frac{k_p}{T_i}}{s^2}$$

(2.2)

Para la función de transferencia de lazo cerrado, se tiene la ecuación 2.3. En donde  $\theta_{PLL}$  corresponde al ángulo de fase resultante obtenido del PLL y  $\theta_{grid}$  en ángulo de fase de la red inyectada al algoritmo. Esta ecuación se tiene, ya que el sistema es Single Input Single Output (SISO).

$$\begin{split} \frac{\theta_{PLL}}{\theta_{grid}} &= \frac{LF(s)}{s + LF(s)} \\ &= \frac{k_p * (1 + \frac{1}{s * T_i})}{s + (k_p * (1 + \frac{1}{s * T_i}))} \\ &= \frac{k_p s + \frac{k_p}{T_i}}{s^2 + k_p s + \frac{k_p}{T_i}} \end{split} \tag{2.3}$$

Para normalizar las ecuaciones de segundo orden obtenidas de las funciones de transferencia, se considera las expresiones 2.4 y 2.5, considerando que  $\omega_n$  es la frecuencia natural de oscilación, que es la frecuencia en donde se da el sobreimpulso y  $\xi$  es el factor de amortiguamiento del sistema.

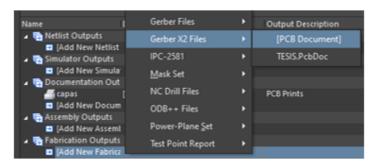

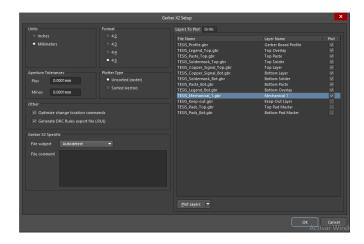

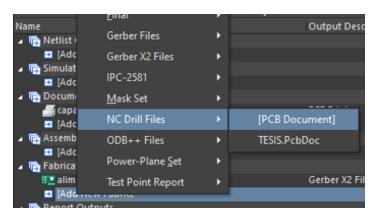

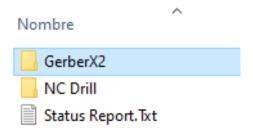

$$\omega_n = \sqrt{\frac{k_p}{T_i}} \tag{2.4}$$