## UNIVERSIDAD DE CUENCA

## FACULTAD DE INGENIERÍA

ESCUELA DE INGENIERÍA ELECTRÓNICA Y TELECOMUNICACIONES

MEMORIA TÉCNICA DEL PROYECTO DE TITULACIÓN "IMPLEMENTACIÓN DE TÉCNICAS DE COMUNICACIONES DIGITALES SOBRE UN DISPOSITIVO FPGA"

UNIVERSIDAD DE CUENCA

Proyecto previo a la obtención del título de Ingeniero en Electrónica y Telecomunicaciones

Autores:

Luis David García Ruiz. Paúl Xavier Verdugo Ríos.

Director:

Ing. Kenneth Samuel Palacio Baus, MSc.

Co-Director:

Ing. Lizandro Damian Solano Quinde, PhD.

Cuenca - Ecuador 2016

#### Resumen

Palabras clave: FPGA, Moduladores, Sistemas Digitales, Radio Definida por Software (SDR), GNU Radio.

Los sistemas de comunicación cuentan con varias etapas, siendo una de las más importantes, aquella relacionada con la modulación de señales. En este proyecto se explora la implementación de diferentes esquemas de modulación digital sobre un dispositivo de tipo FPGA con el objetivo de mostrar su versatilidad en el contexto de su uso en el desarrollo de sistemas de telecomunicaciones gracias a sus características propias de ser reconfigurable y altamente flexible. Es así que se implementan los esquemas de modulación ASK, FSK, PSK y QAM sobre la tarjeta de desarrollo sobre FPGA Spartan 3E de Xilinx, como parte de un sistema integral que incluye una etapa de amplificación y acople de radio frecuencia para transmitir señales de manera inalámbrica.

En este contexto, y con el fin de evaluar la efectividad de los sistemas de modulación implementados, se hace uso del software GNU Radio, que constituye una herramienta de código abierto para el desarrollo y experimentación con sistemas de comunicaciones. Su uso se enfoca en la evaluación de la funcionalidad del modulador implementado sobre el FPGA para las diferentes posibilidades evaluadas. Mediante aplicación de distintos procesos experimentales, se logra evaluar la tasa de error en la transmisión de datos para cada modulación, para transmisiones realizadas sobre una fuente de datos determinada y con un intervalo de confianza de 95 %. La información transmitida es procesada en un computador personal mediante Matlab, lo que favorece el análisis de los resultados obtenidos.

David García R., Paúl Verdugo R.

### **Abstract**

**Keywords:** FPGA, Modulators, Digital Systems, Software Defined Radio (SDR), GNU Radio.

Communication systems comprise several stages being the stage related to input signal modulation, one of the most important phases. This project explores the implementation of different modulation schemes on an FPGA device from the manufacturer Xilinx, in order to show its versatility related to making use of this type of devices in developing telecommunication systems given its flexibility feature. Thus, ASK, FSK, PSK and QAM modulations are implemented over a Spartan 3E development board as part of an integrated system which includes a radio frequency amplification and coupling stage that enables the system to transmit signals wirelessly.

In this context and aiming to evaluated the performance of the implemented modulation schemes, we make use of the GNU Radio software, which comprises a set of tools focused on testing, learning and developing communication systems. This software is employed to test our modulations implementation by the definition of different experimental processes that yield an estimation of bit error rates within a confidence interval of 95%. Received information is processed at a personal computer running Matlab which support our results analysis.

David García R., Paúl Verdugo R.

# Índice general

|    | Resu | ımen .  |                                             | 2          |

|----|------|---------|---------------------------------------------|------------|

|    | Abst | tract.  |                                             | 4          |

|    | Índi | ce gene | ral                                         | 6          |

|    | ,    |         | guras                                       | 9          |

|    | ,    |         | ablas                                       | 12         |

| 1. | Intr | oducci  | ión                                         | 31         |

|    | 1.1. | Plante  | eamiento del Problema                       | 31         |

|    | 1.2. |         | vos                                         | 33         |

|    |      | 1.2.1.  |                                             | 33         |

|    |      |         | Objetivos Específicos                       | 33         |

| 2  | Two  | haina I | Relacionados                                | 35         |

| ۷. | Ha   | vajos i | telacionados                                | <b>3</b> 0 |

| 3. | Des  | arrollo | del Sistema                                 | 39         |

|    | 3.1. | Esque   | mas de Modulación Digital                   | 39         |

|    |      | 3.1.1.  | Modulación por Desplazamiento de Amplitud   | 39         |

|    |      | 3.1.2.  | Modulación por Desplazamiento de Frecuencia | 40         |

|    |      | 3.1.3.  | Modulación por Desplazamiento de Fase       | 42         |

|    |      | 3.1.4.  | Modulación de Amplitud en Cuadratura        | 44         |

|    | 3.2. | Desarr  | collo del Transmisor                        | 46         |

|    |      | 3.2.1.  | Field Programmable Gate Array               | 47         |

|    |      | 3.2.2.  | Conversor Digital-Analógico - DAC           | 48         |

|    |      | 3.2.3.  | Amplificación de Radiofrecuencia $RF$       | 52         |

|    | 3.3. | Impler  | mentación de Modulaciones Digitales en FPGA | 53         |

|    |      | 3.3.1.  | Generación de portadora                     | 53         |

|    |      | 3.3.2.  | Modulación 2-ASK                            | 54         |

|    |      | 3.3.3.  | Modulación 4-ASK                            | 56         |

|    |      | 3.3.4.  | Modulación 8-ASK                            | 58         |

|                     |       | 3.3.5.  | Modulación 2-FSK                                              | 60    |

|---------------------|-------|---------|---------------------------------------------------------------|-------|

|                     |       | 3.3.6.  | Modulación 2-PSK                                              | 62    |

|                     |       | 3.3.7.  | Modulación 4-PSK                                              | 63    |

|                     |       | 3.3.8.  | Modulación 8-PSK                                              | 65    |

|                     |       | 3.3.9.  | Modulación 16-QAM                                             | 67    |

|                     | 3.4.  | Desarr  | rollo del Receptor                                            | 69    |

|                     |       | 3.4.1.  | Implementación del Sistema de Recepción                       | . 70  |

|                     |       | 3.4.2.  | Software GNU Radio                                            | . 72  |

|                     | 3.5.  | Imple   | mentación de Demoduladores a través de <i>GNU</i>             |       |

|                     |       | Radio   | $Companion \dots \dots \dots \dots \dots \dots$               | . 78  |

|                     |       | 3.5.1.  | Demodulador de Desplazamiento por Frecuen-                    |       |

|                     |       |         | $\operatorname{cia}, FSK \dots \dots \dots \dots \dots \dots$ | . 78  |

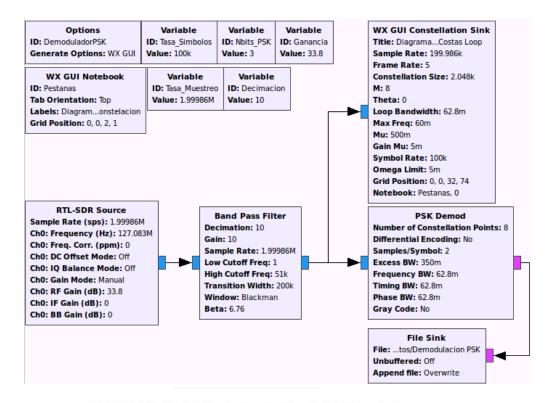

|                     |       | 3.5.2.  | Demodulador de Desplazamiento de Fase, PSI                    | K 80  |

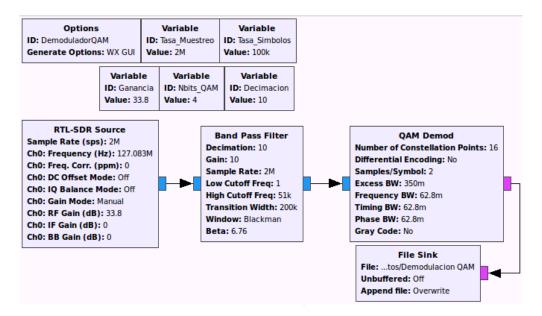

|                     |       | 3.5.3.  | Demodulador de Amplitud en Cuadratura, $QA$                   | M 83  |

|                     |       | 3.5.4.  | Demodulador de Desplazamiento Amplitud,                       |       |

|                     |       |         | ASK                                                           | 85    |

|                     |       |         |                                                               |       |

| 4.                  |       |         | n del Sistema                                                 | 93    |

|                     | 4.1.  |         | dimiento para la Realización de Pruebas y Me-                 |       |

|                     |       | dicion  |                                                               | . 93  |

|                     |       | 4.1.1.  | Protocolo para la Realización del Primer Ex-                  |       |

|                     |       |         | perimento                                                     | . 94  |

|                     |       | 4.1.2.  | 1                                                             |       |

|                     |       |         | perimento                                                     |       |

|                     | 4.2.  |         | ación Cuantitativa                                            |       |

|                     |       |         | Evaluación del Experimento 1                                  |       |

|                     |       | 4.2.2.  | Evaluación del Experimento 2                                  | . 118 |

| <b>5</b> .          | Cor   | clusio  | nes y Trabajos Futuros                                        | 135   |

|                     | 5.1.  | Concl   | $usiones \dots \dots \dots \dots \dots$                       | 135   |

|                     | 5.2.  | Traba   | jos Futuros                                                   | 136   |

| Aı                  | iexo  | S       |                                                               | 138   |

| $\operatorname{Bi}$ | bliog | grafía. |                                                               | 147   |

## Índice de figuras.

| 1.1.  | Esquema de transmisión planteado                            | 32 |

|-------|-------------------------------------------------------------|----|

| 3.1.  | Modulación digital ASK. Imagen tomada de [24]               | 40 |

| 3.2.  | Esquema de un modulador ASK. Imagen tomada de               |    |

|       | [34]                                                        | 40 |

| 3.3.  | Modulación digital FSK. Imagen tomada de [24]               | 41 |

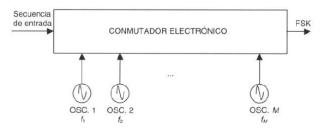

| 3.4.  | Generación de FSK mediante conmutador electróni-            |    |

|       | co. Imagen tomada de [34]                                   | 41 |

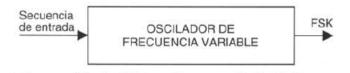

| 3.5.  | Generación de FSK mediante oscilador de frecuencia          |    |

|       | variable. Imagen tomada de [34]                             | 42 |

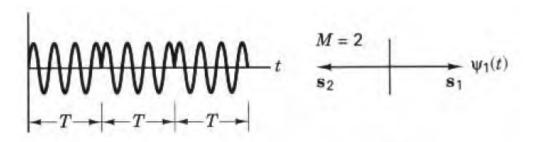

| 3.6.  | Modulación digital PSK. Imagen tomada de [24]               | 43 |

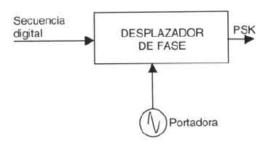

| 3.7.  | Generación de PSK mediante oscilador de frecuencia          |    |

|       | variable. Imagen tomada de [34]                             | 43 |

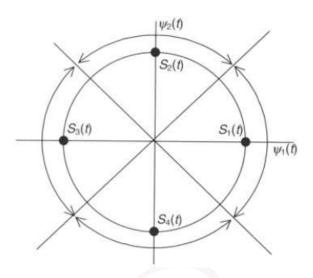

| 3.8.  | Diagrama vectorial de una modulación 4-PSK. Ima-            |    |

|       | gen tomada de [34]                                          | 44 |

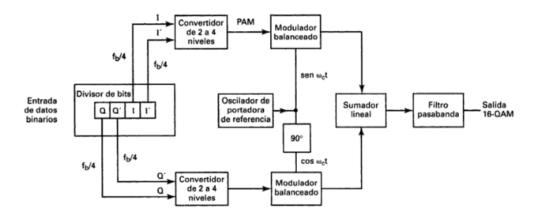

| 3.9.  | Diagrama transmisor 16-QAM. Imagen tomada de [29].          | 44 |

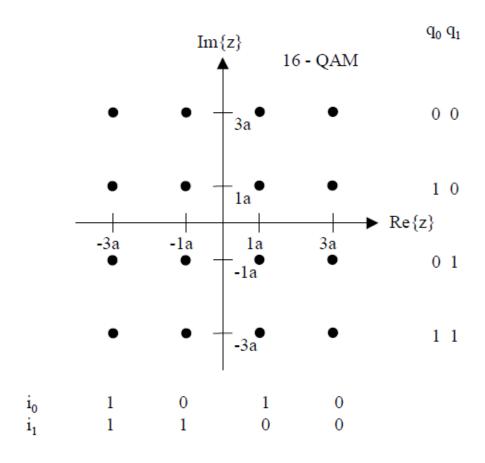

| 3.10. | Diagrama de constelación de 16-QAM. $i_0$ e $i_1$ indican   |    |

|       | el mapeo de amplitud en fase y $q_0$ y $q_1$ indican el     |    |

|       | mapeo de amplitud en cuadratura. Imagen tomada              |    |

|       | de [11]                                                     | 45 |

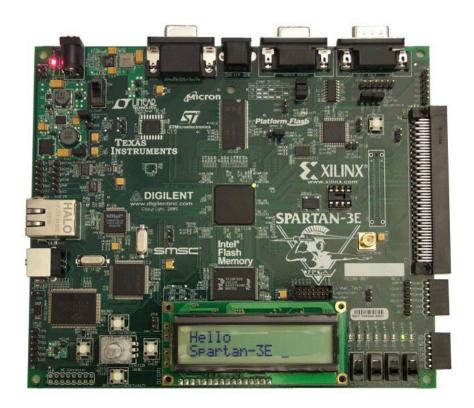

| 3.11. | Spartan 3E starter kit de Xilinx                            | 48 |

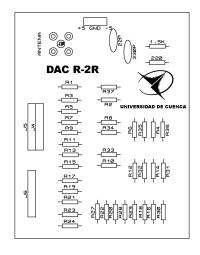

| 3.12. | DAC R-2R. Figura tomada de Proteus 8.0                      | 50 |

|       | Señal tipo seno muestreada                                  | 51 |

| 3.14. | Filtro pasabajos de segundo orden Sallen y Key. <i>Ima-</i> |    |

|       | gen tomada de [15]                                          | 52 |

| 3.15. | Señal sinusoidal generada con el FPGA                       | 54 |

| 3.16. | Señal modulada 2-ASK                                        | 55 |

| 3.17. | Señal modulada 2-ASK en el dominio de la frecuencia.        | 56 |

|       |                                                             |    |

| 3.18.        | Señal modulada 4-ASK                                  | 57  |

|--------------|-------------------------------------------------------|-----|

| 3.19.        | Señal modulada 4-ASK en el dominio de la frecuencia.  | 58  |

| 3.20.        | Señal modulada 8-ASK                                  | 59  |

| 3.21.        | Señal modulada 8-ASK en el dominio de la frecuencia.  | 60  |

| 3.22.        | Señal modulada 2-FSK                                  | 61  |

| 3.23.        | Señal modulada 2-FSK en el dominio de la frecuencia.  | 61  |

| 3.24.        | Señal modulada 2-PSK                                  | 62  |

| 3.25.        | Señal modulada 2-PSK en el dominio de la frecuencia.  | 63  |

| 3.26.        | Señal modulada 4-PSK                                  | 64  |

| 3.27.        | Señal modulada 4-PSK en el dominio de la frecuencia.  | 64  |

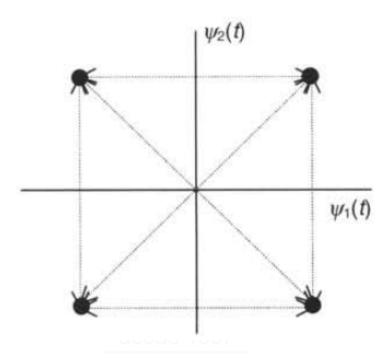

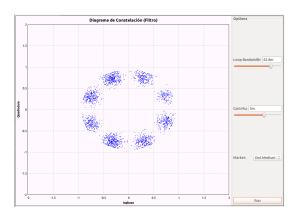

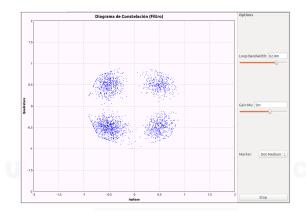

| 3.28.        | Diagrama de constelacion 4-PSK                        | 65  |

| 3.29.        | Señal modulada 8-PSK                                  | 66  |

| 3.30.        | Diagrama de constelacion 8-PSK                        | 66  |

| 3.31.        | Señal modulada 8-PSK en el dominio de la frecuencia.  | 67  |

| 3.32.        | Señal modulada 16-QAM                                 | 68  |

| 3.33.        | Espectro de frecuencias de modulación 16-QAM          | 69  |

| 3.34.        | Sistema receptor basado en GNU Radio                  | 70  |

| 3.35.        | Configuración del bloque RTL-SDR de GNU-RADIO.        |     |

|              | Se muestran las configuraciones establecidas para el  |     |

|              | hardware receptor SDR                                 | 73  |

| 3.36.        | Configuración del bloque de filtro pasa banda de GNU- |     |

|              | RADIO. Se muestran las configuraciones establecidas   |     |

| 2 2 <b>=</b> | para el filtro.                                       | 75  |

| 3.37.        | Bloques generadores de gráficas y sus parámetros con- |     |

| 0.00         | figurables                                            | 77  |

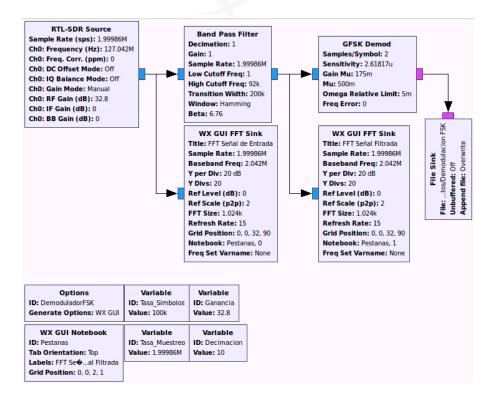

| 3.38.        | Implementación del demodulador FSK mediante el        | 70  |

| 2 20         | uso del bloque $Demod\ GFSK$                          | 79  |

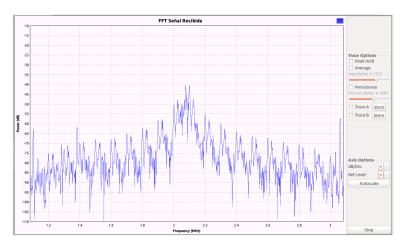

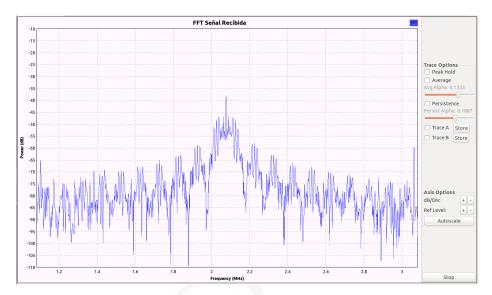

|              | FFT de una señal 4-PSK recibida                       | 81  |

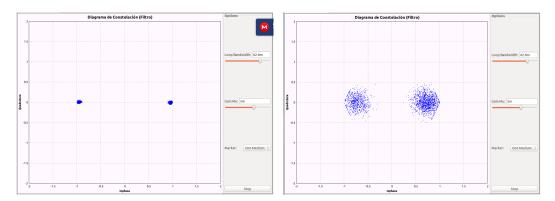

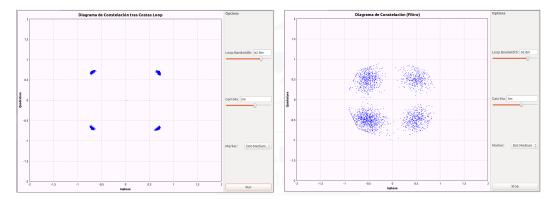

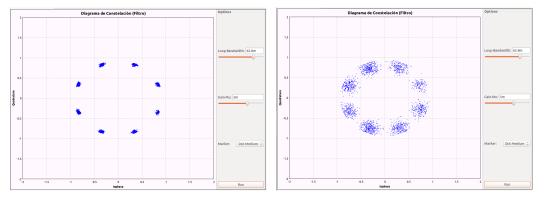

| 3.40.        | Diagramas de constelación para 2,4 y 8 PSK a dife-    | 00  |

| 9 41         | rentes distancias                                     | 82  |

| 3.41.        | Implementación del demodulador PSK mediante el        | 02  |

| 2 40         | uso del bloque $Demod PSK$                            | 83  |

| 5.42.        | Implementación del demodulador QAM mediante el        | Q A |

| 9 49         | uso del bloque $Demod\ PSK$                           | 84  |

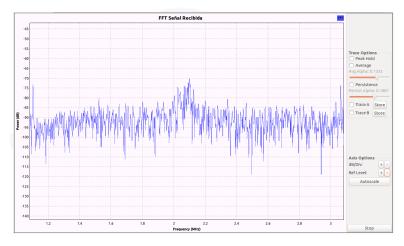

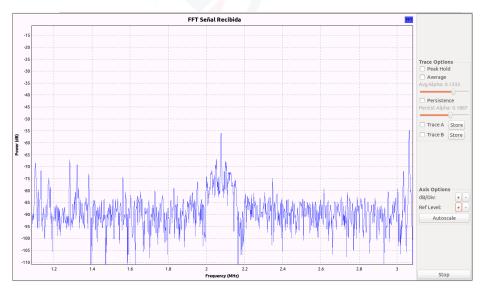

| ა.4ა.        | FFT de una señal 16-QAM recibida a una distancia      | Q A |

|              | de 40cm                                               | 84  |

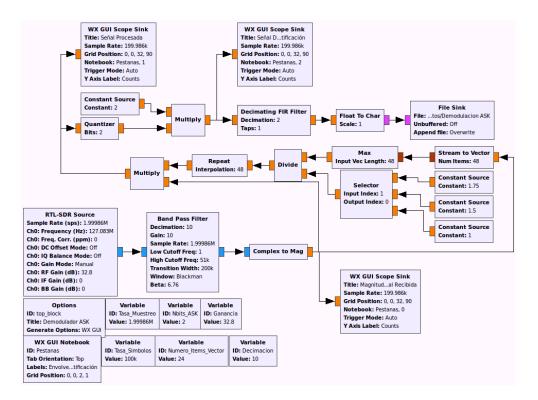

| 3.44. | Implementación del demodulador ASK mediante el                        |       |

|-------|-----------------------------------------------------------------------|-------|

|       | uso de diferentes bloques de $GRC$                                    | . 85  |

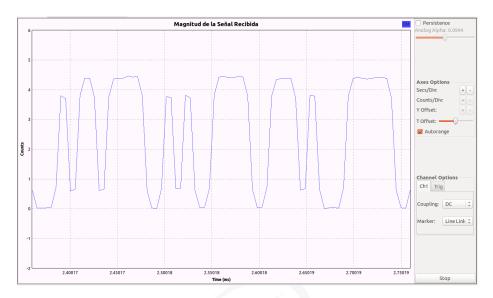

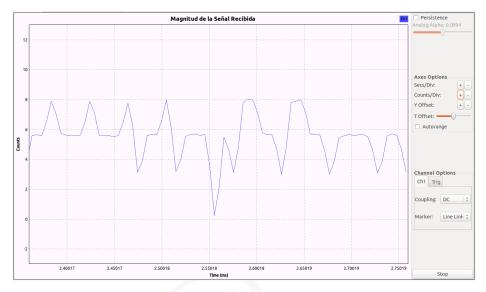

| 3.45. | Magnitud de la señal recibida ASK                                     | . 86  |

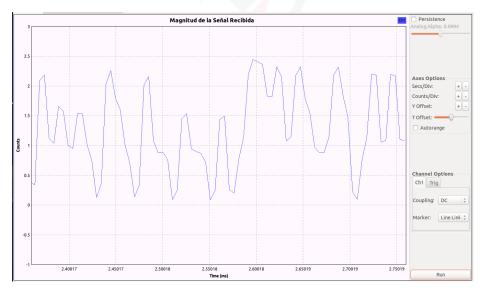

| 3.46. | Magnitud de la señal recibida ASK                                     | . 89  |

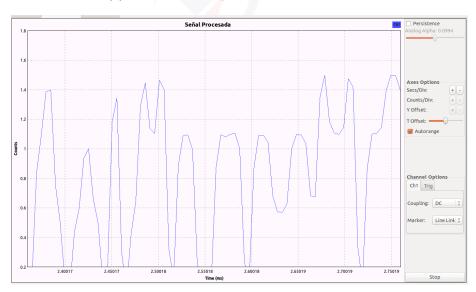

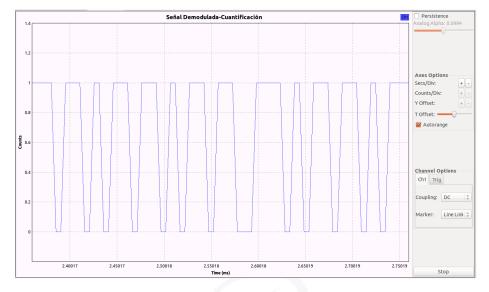

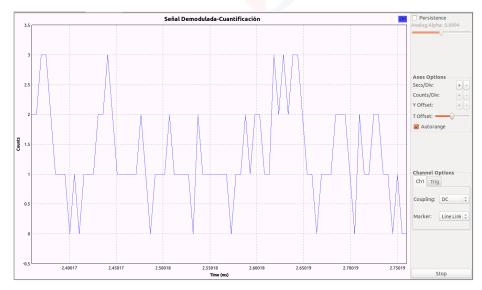

| 3.47. | Demodulación de señales ASK                                           | . 90  |

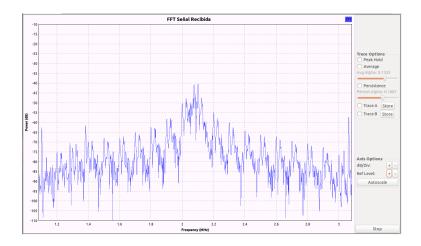

| 3.48. | FFT de señal ASK recibida                                             | . 91  |

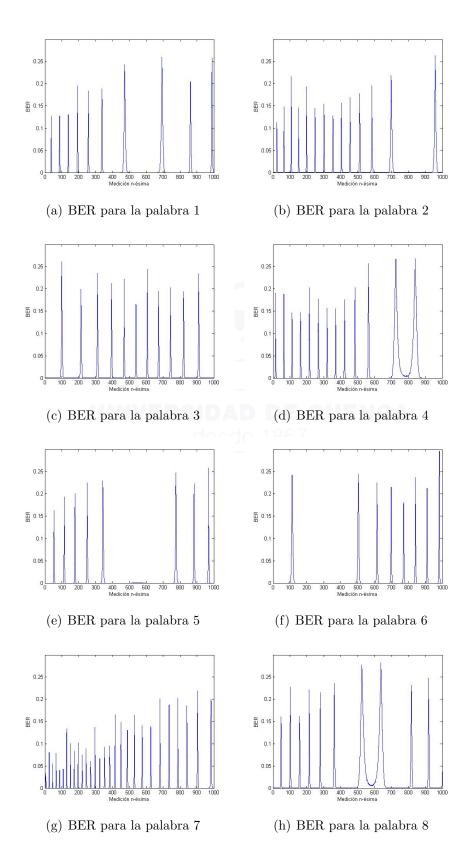

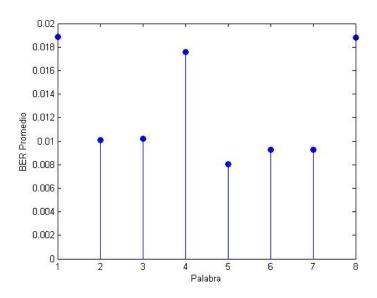

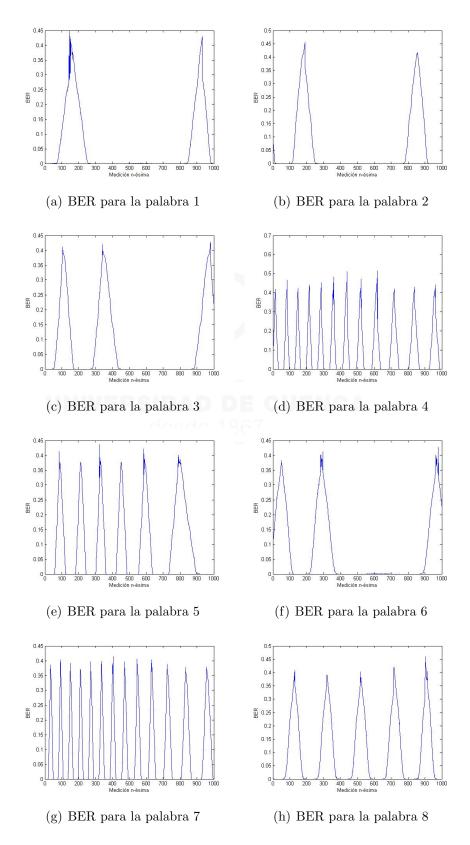

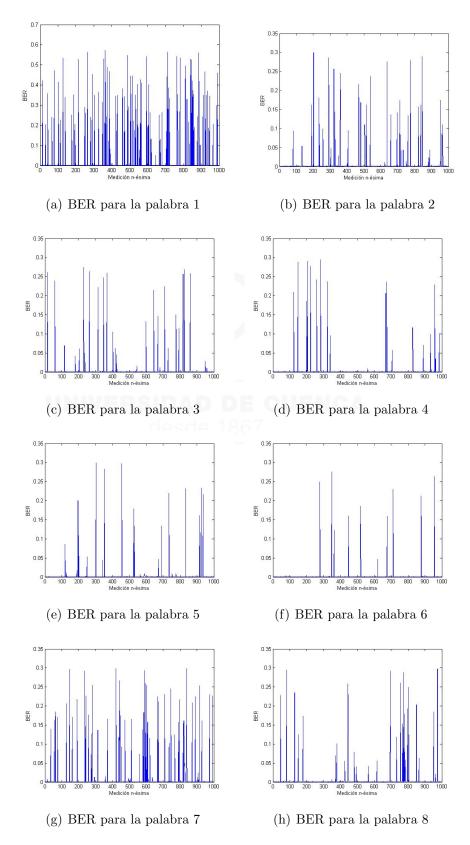

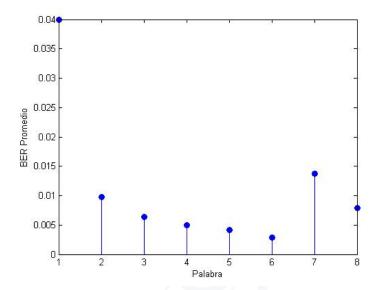

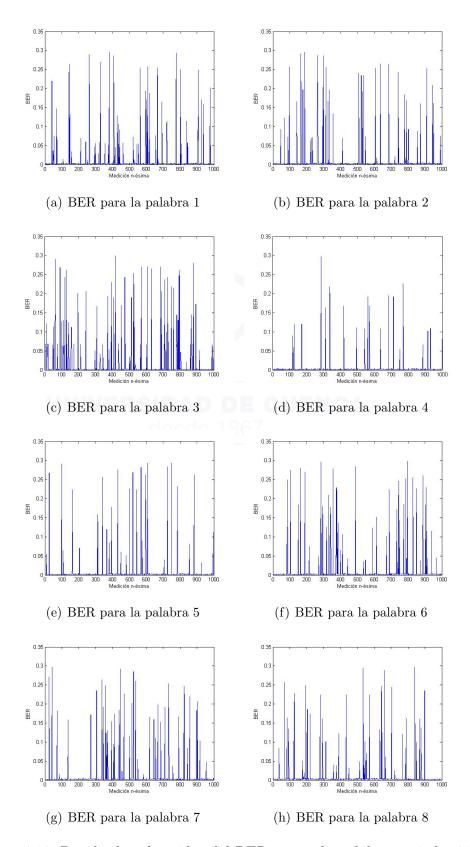

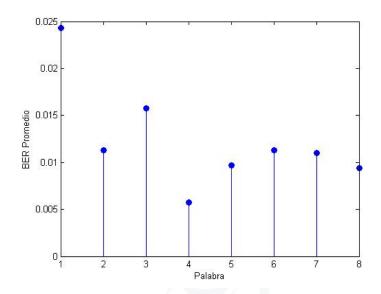

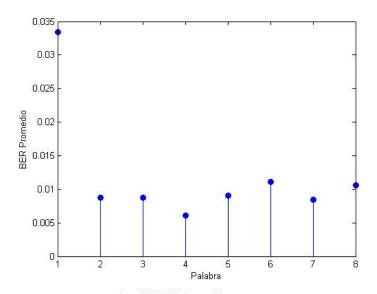

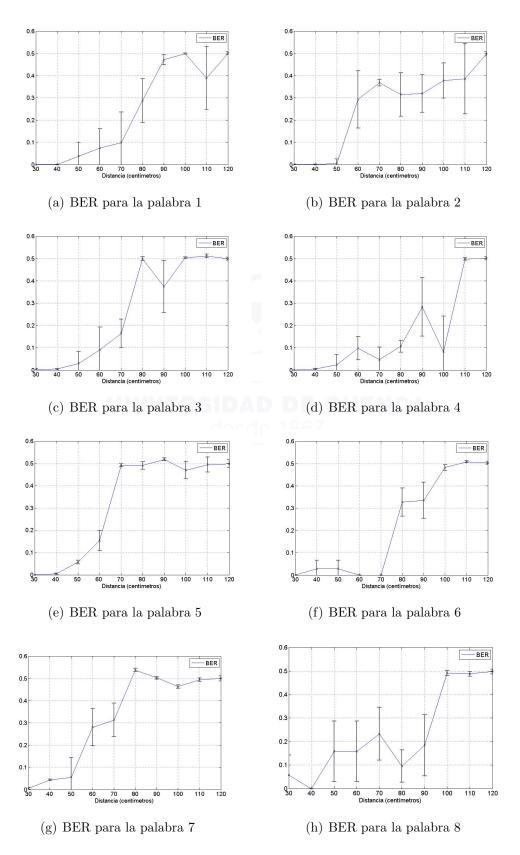

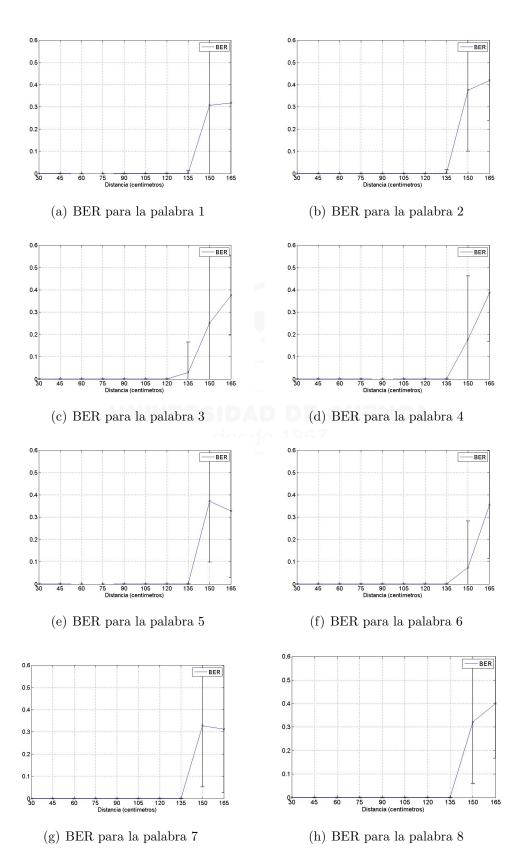

| 4.1.  | Resultados obtenidos del BER por cada palabra enviada, 2-ASK          | . 98  |

| 4.2.  | Resultados Obtenidos del BER promedio por cada                        |       |

| 4.3.  | palabra enviada, 2-ASK                                                |       |

| 4.4.  | viada, 4-ASK                                                          | . 101 |

| 4 5   | palabra enviada, 4-ASK                                                | . 102 |

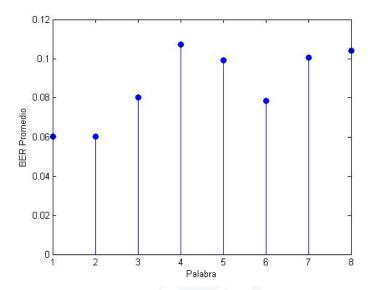

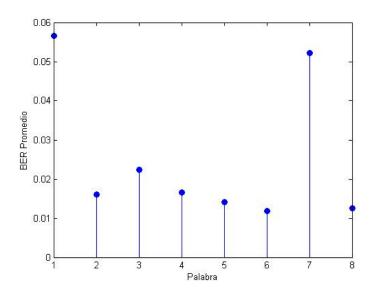

| 4.5.  | Resultados obtenidos del BER por cada palabra enviada, 2-PSK          | . 104 |

| 4.6.  | Resultados Obtenidos del BER promedio por cada palabra enviada, 2-PSK | . 105 |

| 4.7.  | Resultados obtenidos del BER por cada palabra enviada, 4-PSK          |       |

| 4.8.  | Resultados Obtenidos del BER promedio por cada palabra enviada, 4-PSK |       |

| 4.9.  | Comparación de diagramas de constelación de 2, 4                      | . 100 |

|       | y 8-PSK a una distancia de 190cm, 164cm y 100cm respectivamente       | . 110 |

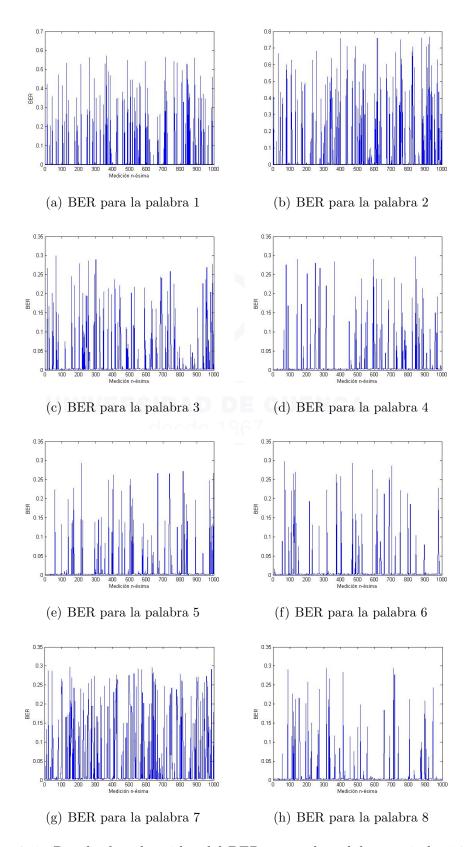

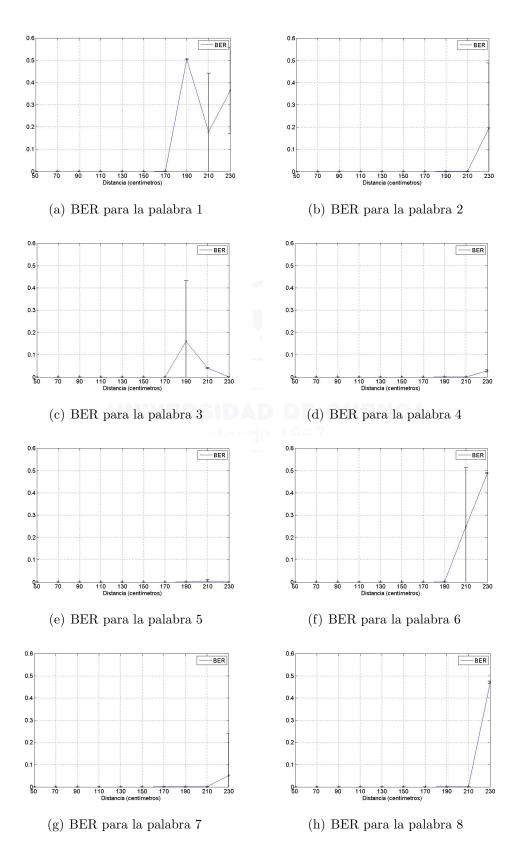

| 4.10. | Resultados obtenidos del BER por cada palabra enviada, 8-PSK          | . 111 |

| 4.11. | Resultados Obtenidos del BER promedio por cada palabra enviada, 8-PSK | 119   |

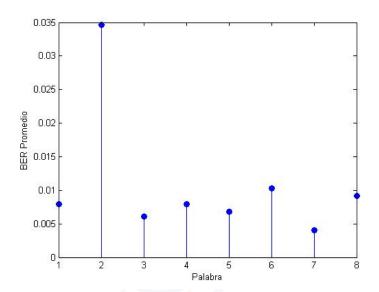

| 4.12. | Resultados obtenidos del BER por cada palabra en-                     |       |

| 1 19  | viada, 2-FSK                                                          | . 114 |

|       | Resultados Obtenidos del BER promedio por cada palabra enviada, 2-FSK | . 115 |

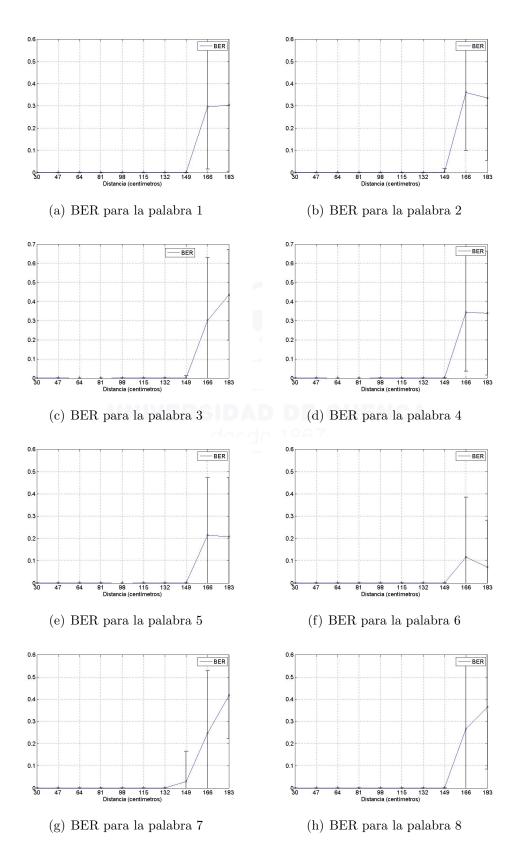

| 4.14. | Resultados Obtenidos del BER promedio por cada palabra enviada, 16QAM | . 116 |

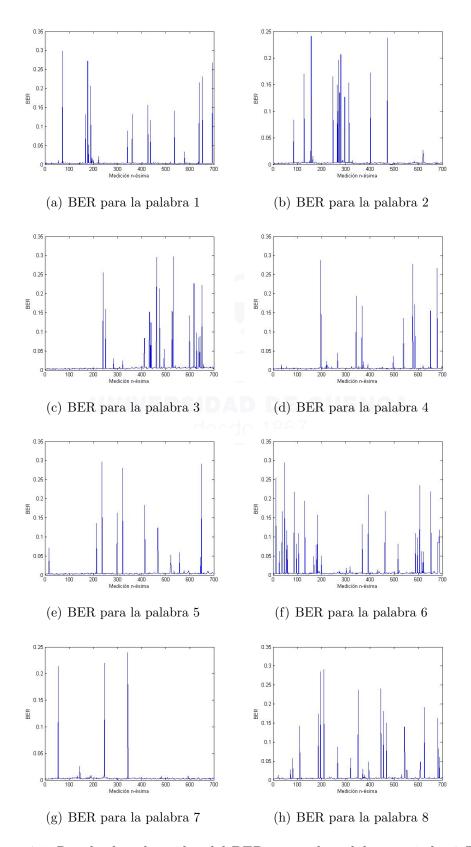

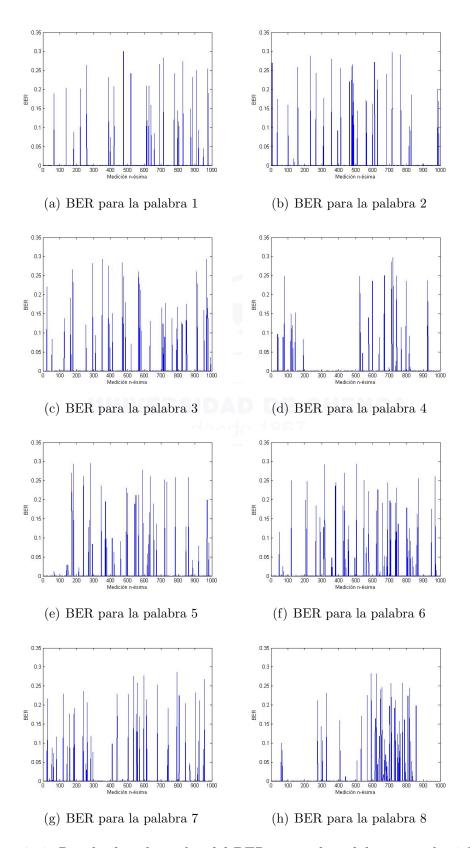

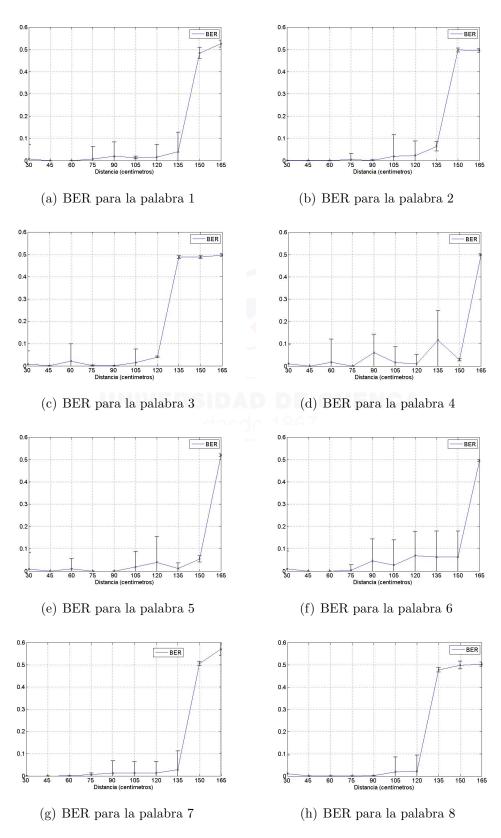

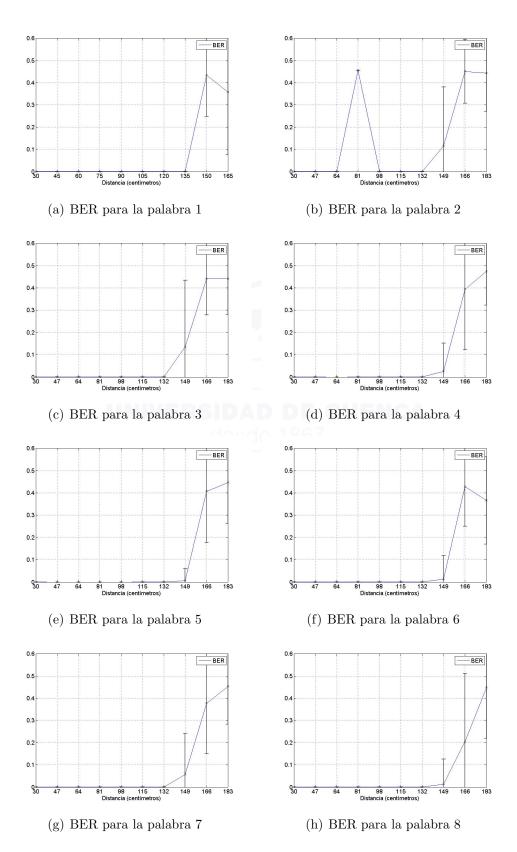

| 4.15. | Resultados obtenidos del BER por cada palabra en-      |

|-------|--------------------------------------------------------|

|       | viada, 16-QAM                                          |

| 4.16. | Resultados obtenidos del BER con diferentes distan-    |

|       | cias entre emisor y receptor por cada palabra enviada, |

|       | 2-ASK                                                  |

| 4.17. | Resultados obtenidos del BER con diferentes distan-    |

|       | cias entre emisor y receptor por cada palabra enviada, |

|       | 4-ASK                                                  |

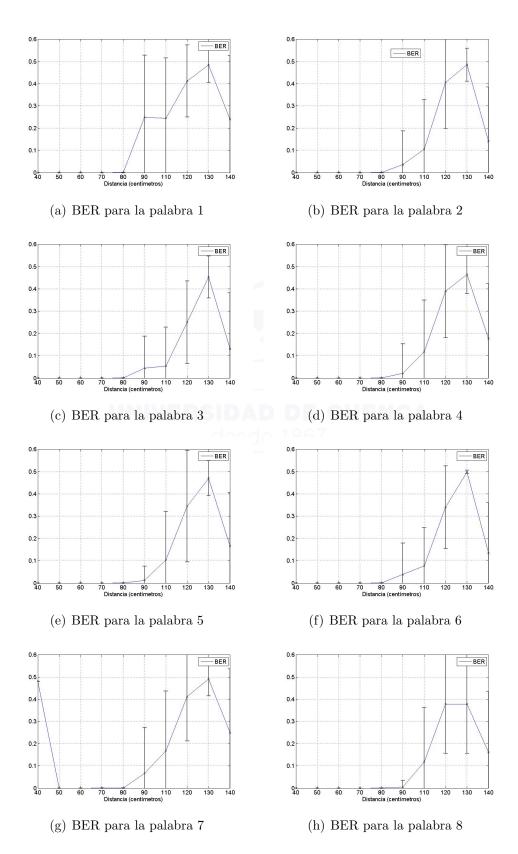

| 4.18. | Resultados obtenidos del BER por cada palabra en-      |

|       | viada, 2-PSK                                           |

| 4.19. | Resultados obtenidos del BER por cada palabra en-      |

|       | viada, 4-PSK                                           |

| 4.20. | Resultados obtenidos del BER por cada palabra en-      |

|       | viada, 8-PSK                                           |

| 4.21. | Resultados obtenidos del BER por cada palabra en-      |

|       | viada, 2-FSK                                           |

| 4.22. | Resultados obtenidos del BER por cada palabra en-      |

|       | viada, 16-QAM                                          |

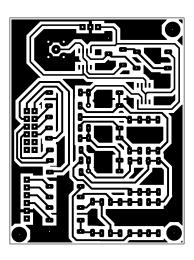

| 5.1.  | Esquema TOP del conversor R-2R                         |

| 5.2.  | Esquema Bottom del conversor R-2R                      |

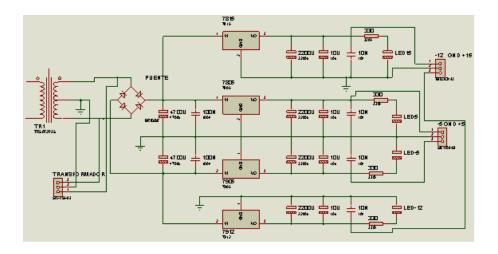

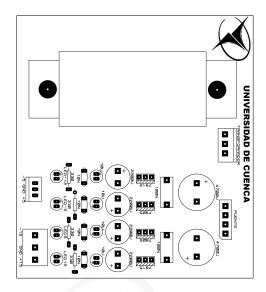

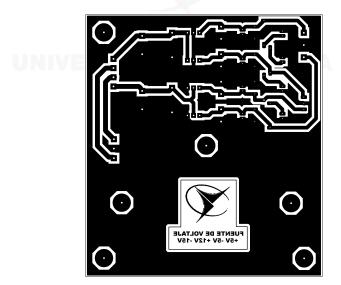

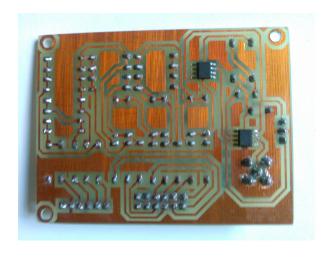

| 5.3.  | Esquema de Fuente simétrica de voltaje                 |

| 5.4.  | Esquema TOP de la fuente de alimentación 141           |

| 5.5.  | Esquema Bottom de la fuente de alimentación 141        |

| 5.6.  | Conector Digilent Hirose de 100 pines                  |

| 5.7.  | Amplificador de rafiofrecuencia                        |

| 5.8.  | Receptor de televisión digital y radio FM 143          |

| 5.9.  | Convertidor de Frecuencias                             |

| 5.10. | Vista superior del conversor R-2R                      |

|       | Vista inferior del conversor R-2R                      |

|       | Fuente simétrica de voltaje                            |

| 5.13. | Transmisor de modulaciones digitales                   |

| 5.14. | Receptor de modulaciones digitales                     |

## Índice de tablas.

| 3.1. | Equivalencia binario-decimal                              | 56  |

|------|-----------------------------------------------------------|-----|

| 3.2. | equivalencia binario-decimal en 8-ASK                     | 58  |

| 3.3. | Tabla de verdad convertidor canal $I$                     | 67  |

| 3.4. | Tabla de verdad convertidor canal $Q \ldots \ldots$       | 67  |

| 3.5. | Potencias de salida del amplificador de radio frecuencia. | 69  |

| 3.6. | Valores de Ganancias Configurables para el Receptor       |     |

|      | SDR                                                       | 72  |

| 3.7. | Cuantificación según rangos de valores de entrada al      |     |

|      | bloque $Quantizer$ de $GRC$                               | 87  |

| 4.1. | Resultados del promedio del BER para 2-ASK por            |     |

|      | palabra en porcentaje                                     | 99  |

| 4.2. | Resultados del promedio del BER para 4-ASK por            |     |

|      | palabra en porcentaje                                     | 00  |

| 4.3. | Resultados del promedio del BER para 2-PSK por            |     |

|      | palabra en porcentaje                                     | 05  |

| 4.4. | Resultados del promedio del BER para 4-PSK por            |     |

|      | palabra en porcentaje                                     | .06 |

| 4.5. | Resultados del promedio del BER para 8-PSK por            |     |

|      | palabra en porcentaje                                     | 12  |

| 4.6. | Resultados del promedio del BER para FSK por pa-          |     |

|      | labra en porcentaje                                       | 15  |

| 4.7. | Resultados del promedio del BER para QAM por pa-          |     |

|      | labra en porcentaje                                       | 16  |

Yo, Luis David García Ruiz, autor de la tesis Implementación de técnicas de comunicaciones digitales sobre un dispositivo FPGA, certifico que todas las ideas, opiniones, y contenidos expuestos en la presente investigación, son de exclusiva responsabilidad de sus autores.

Cuenca, Octubre 2016.

Luis David García Ruiz C.I. 0105073779

Yo, Paúl Xavier Verdugo Ríos, autor de la tesis Implementación de técnicas de comunicaciones digitales sobre un dispositivo FPGA, certifico que todas las ideas, opiniones, y contenidos expuestos en la presente investigación, son de exclusiva responsabilidad de sus autores.

Cuenca, Octubre 2016.

Paúl Xavier Verdugo Ríos

C.I. 0105088090

Yo, Luis David García Ruiz, autor de la tesis Implementación de técnicas de comunicaciones digitales sobre un dispositivo FPGA, reconozco y acepto el derecho de la Universidad de Cuenca, en base al Art. 5 literal c) de su Reglamento de Propiedad Intelectual, de publicar este trabajo por cualquier medio conocido o por conocer, al ser este requisito para la obtención de mi título de Ingeniero en Electrónica y Telecomunicaciones. El uso que la Universidad de Cuenca hiciere de este trabajo, no implicará afección alguna de mis derechos morales o patrimoniales como autor.

Cuenca, Octubre 2016.

Luis David García Ruiz

C.I. 0105073779

Yo, Paúl Xavier Verdugo Ríos, autor de la tesis Implementación de técnicas de comunicaciones digitales sobre un dispositivo FPGA, reconozco y acepto el derecho de la Universidad de Cuenca, en base al Art. 5 literal c) de su Reglamento de Propiedad Intelectual, de publicar este trabajo por cualquier medio conocido o por conocer, al ser este requisito para la obtención de mi título de Ingeniero en Electrónica y Telecomunicaciones. El uso que la Universidad de Cuenca hiciere de este trabajo, no implicará afección alguna de mis derechos morales o patrimoniales como autor.

Cuenca, Octubre 2016.

Paúl Xavier Verdugo Ríos

C.I. 0105088090

#### **CERTIFICO**

Que el presente proyecto de titulación: Implementación de técnicas de comunicaciones digitales sobre un dispositivo FPGA fue dirigido por mi persona.

Cuenca, Octubre 17 de 2016.

Ing. Kenneth Samuel Palacio Baus, MSc. Director de Poyecto de Titulación

#### **CERTIFICO**

Que el presente proyecto de titulación: Implementación de técnicas de comunicaciones digitales sobre un dispositivo FPGA fue co-dirigido por mi persona.

Ing. Lizandro Damian Solano-Quinde, PhD. Co-Director de Proyecto de Titulación

## Agradecimientos

Agradecemos a nuestros directores de tesis, Ing. Kenneth Palacio e Ing. Lizandro Solano, por el apoyo económico y académico, la confianza, y dedicación de tiempo. Con sus conocimientos nos orientaron en la correcta realización de este proyecto.

Agradecemos también a nuestros profesores, quienes a lo largo de la carrera nos han formado para ser buenos profesionales. Ustedes nos motivaron a lograr nuestras metas.

Agradecemos de manera especial a los ingenieros, Remigio Guevara y Luis Gonzales, por su apoyo al brindarnos los equipos necesarios para realizar el proyecto.

## Dedicatoria

A mis padres Rubén y Jenny por estar siempre presentes como ejemplo de perseverancia, por su comprensión, amor y ayuda en los momentos difíciles. A mi hermano Dario por su apoyo incondicional y siempre estar a mi lado para compartir conmigo triunfos y fracasos. Todo este trabajo ha sido posible gracias a ellos.

David García.

#### UNIVERSIDAD DE CUENCA desde 1867

Dedico esta tesis a Dios, por permitirme cumplir mis logros y metas. A mi enamorada, Fernanda, por todo el amor que me diste y por tu incondicional apoyo durante la realización de este proyecto de titulación. Siempre que pudiste me animaste a seguir adelante. A mis padres, que estuvieron a mi lado durante todo este tiempo, dándome fuerza para continuar. A mis amigos, quienes ayudaron en la culminación de este proyecto.

Paúl Verdugo.

## Capítulo 1

## Introducción

Actualmente, el desarrollo de sistemas de telecomunicaciones está basado, en el uso de técnicas de transmisión digitales, por su versatilidad en incorporar, técnicas de codificación, corrección de errores, sincronización y el ajuste adaptativo de la potencia de transmisión, propiciando un eficiente consumo de energía [21]. Un ejemplo de esta tendencia se evidencia en las transmisiones de televisión abierta y radio, que han migrado hacia estándares digitales. Particularmente, en el caso de la transmisión de televisión, en Ecuador y otros países de la región, se ha adoptado en años recientes el estándar ISDB-Tb.

En la ingeniería de telecomunicaciones, el estudio de estas técnicas se fundamenta en la comprensión de los fundamentos matemáticos y prácticos vinculados a su funcionamiento, para lo cual se ha propuesto el uso de diversas plataformas de hardware. Estas plataformas posibilitan la implementación de sistemas de modulación, codificación y multiplexación digitales, como por ejemplo, aquellas basadas en la tecnología SDR (Software Defined Radio).

En este proyecto se plantea implementar la etapa de modulación de un sistema de comunicaciones digitales, de tal modo que se disponga de un bloque componente utilizable en el desarrollo futuro de sistemas de transmisión de información basados en SDR y Radio Digital, tanto a nivel académico como comercial.

#### 1.1. Planteamiento del Problema

La implementación de la etapa de modulaciones de un sistema de comunicaciones digital contempla la transmisión y recepción de señales mediante técnicas

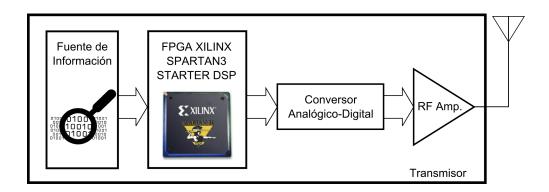

de transmisión digital, donde la etapa de modulación se soporta en un dispositivo FPGA (Field Programmable Gate Array), concretamente haciendo uso de la plataforma *Spartan 3E Starter de Xilinx*. El esquema general del transmisor se ilustra en la Figura 1.1. El esquema presenta una fuente de datos binarios que ingresan al FPGA para ser modulados, luego son pasados a un conversor digital-analógico, la señal es amplificada con un amplificador de radiofrecuencia y es transmitido por la antena.

Figura 1.1: Esquema de transmisión planteado.

Particularmente, los esquemas de modulación que se implementarán son: modulación por desplazamiento de amplitud ASK, modulación por desplazamiento de frecuencia FSK, modulación por desplazamiento de fase PSK y modulación por amplitud en cuadratura QAM, de modo que se pueda evidenciar el potencial de la plataforma Xilinx Spartan 3E como herramienta de complemento del aprendizaje de sistemas de comunicaciones digitales y su utilización en equipos transmisores digitales, al contar con alta flexibilidad y alta velocidad [21] [14] [1] [12] [25].

Con la finalidad de evaluar la implementación de las técnicas de transmisión en el equipo transmisor, se propone el uso de un sistema receptor basado en GNU Radio, que permite recibir las señales transmitidas, procesarlas, graficarlas y almacenarlas en el computador para su posterior análisis. Para ello, se presenta un proceso cuantitativo de evaluación. Esto se hace transmitiendo palabras fijas predefinidas, cada una múltiples veces, a una distancia fija entre antenas emisorreceptor. Entonces se mide la tasa de error de bits. Luego, se obtiene el promedio del BER de cada palabra y se presentan gráficas del promedio del BER de cada palabra. Así se tendrá una idea del comportamiento del sistema transmisor. Otra forma de evaluar será enviando un archivo a diferentes distancias, comenzando

desde una mínima donde la tasa de error de bits promedio al recibir la palabra sea de aproximadamente 0.01, hasta una máxima donde la tasa de error de bits promedio sea alto y así evaluar la validez y comportamiento del sistema en función de la distancia.

## 1.2. Objetivos

#### 1.2.1. Objetivo General

Utilizar un dispositivo FPGA para la implementación de la etapa de modulación en sistemas de comunicaciones digitales.

### 1.2.2. Objetivos Específicos

- 1. Estudiar el uso de dispositivos FPGA para la implementación de sistemas de comunicaciones digitales.

- 2. Implementar técnicas de modulación digital sobre la plataforma FPGA Xilinx Spartan 3E.

- 3. Evaluar el funcionamiento de las técnicas de transmisión implementadas mediante un receptor basado en Software Defined Radio: GNURadio.

## Capítulo 2

## Trabajos Relacionados

Los sistemas de comunicaciones en la actualidad, con la transición de las modulaciones analógicas a digitales, se emplean en múltiples campos como: radar, comunicaciones aeroespaciales y satelitales, comunicaciones navales, marítimas y submarinas, comunicaciones móviles, etc. [19] [14] [12]. Las comunicaciones también se emplean en el campo de la medicina, la cual necesita de altas tasas de datos con alta fidelidad [2]. El avance de las tecnologías en el campo de las telecomunicaciones, hacen necesarios sistemas de comunicaciones más avanzados que hagan mejor uso del espectro, empleando bajas potencias y brindando altas tasas de bits con tasas de error bajas [25] [8].

Las comunicaciones hacen empleo de diferentes tipos de moduladores, constituyendo al modulador como un bloque de alta importancia dentro de los sistemas de comunicación. Los tipos de modulación más básicos utilizados son modulación de amplitud AM, modulación de frecuencia FM, modulación por desplazamiento de amplitud ASK, modulación por desplazamiento de frecuencia FSK y modulación por desplazamiento de fase PSK [12]. Además, una modulación de gran importancia en los sistemas de comunicación es la modulación en cuadratura que es robusta y muy aplicada en comunicaciones satelitales [19].

La necesidad de sistemas de comunicaciones más complejos hace necesario la búsqueda de tecnologías que se acoplen a los estándares actuales. Así, se plantea a un dispositivo FPGA como una alternativa de bajo costo, bajo consumo de potencia y altas tasas de transmisión, para su uso en un sistema de comunicaciones o en una parte del mismo. Múltiples trabajos relacionados al campo de las comunicaciones, específicamente el desarrollo de la etapa de modulación y multiplexación, se han desarrollado sobre dispositivos FPGA.

Modulación PSK en cuadratura ha sido implementada en múltiples trabajos ya que esta tiene la ventaja de poder transmitir altas tasas de datos con potencia reducida y ofrece mayor robustez pues la tasa de error no sufre degradación mientras la eficiencia del ancho de banda es incrementada [19]. Estas altas tasas de datos seguros, son requeridas en aplicaciones como telemedicina, biotelemetría y tratamientos médicos, como se presenta en [5]. QPSK y BPSK también se aplica en observación planetaria. Se han reportado portadoras de 31.250KHz en [19].

Motivos por los que se implementan modulaciones sobre un FPGA son su potencial al ser una herramienta de bajo costo según lo dicho en [14] [1]. Otros trabajos presentan simulaciones acerca del uso de FPGA como una herramienta reconfigurable para la implementación de varias modulaciones con diferentes fuentes de datos. Así, en [21] y [12] se ha mostrado la flexibilidad del FPGA para implementar diferentes tipos de modulaciones sobre el mismo dispositivo, mostrando que el FPGA es un sistema reconfigurable sobre la marcha. En [30] se ha realizado un sistema modulador que puede reconfigurarse en las modulaciones ASK, FSK o PSK. Esto muestra las grandes ventajas del FPGA.

Además de modulaciones, la Multiplexación por División de Frecuencia Ortogonal OFDM, también se ha implementado sobre FPGA. Un importante trabajo presenta la implementación de OFDM basado en el estándar Radio Digital Mundial DRM. Este trabajo es una simulación en el que la mayoria de procesos complejos se realizan en un computador personal, pero es un acercamiento a la implementación de OFDM sobre FPGA [4]. Otros trabajos han simulado e implementado señales OFDM en su totalidad sobre FPGA. En estos trabajos se ha observado el resultado a través de un analizador de espectros. Se ha mostrado que la forma de realizar OFDM es aplicando la transformada inversa de Fourier IFFT [23] [30]. Un trabajo más actual ha implementado una modulación Delta-Sigma DSM sobre FPGA. Este promete ser un transmisor totalmente digital utilizable para aplicaciones SDR. [25]

Varias formas de implementación de modulaciones digitales sobre FPGA se han documentado. Una de las formas principales de hacerlo es a través de Xilinx System Generator, que es una herramienta de Simulink de Matlab<sup>1</sup>. Xilinx System Generator incluye bloques predefinidos para procesamiento digital de señales. Es-

<sup>&</sup>lt;sup>1</sup>Software principalmente matemático para el procesamiento de sistemas.

ta herramienta permite la simulación en un computador personal y la generación del código a ser cargado en un dispositivo FPGA, facilitando la programación de un FPGA [19] [21] [14] [1] [30]. Otra forma de realizar la implementación es a través de la programación directa en VHDL del código que se cargará en el FPGA [12].

En los trabajos [21] [14] [1] [12] [25] se da soporte al hecho de que un FPGA es un dispositivo utilizable en modulaciones, por su alta velocidad, su bajo coste y su bajo uso de recursos para realizar sus propósitos, siendo más apropiados que otros dispositivos, como por ejemplo los microcontroladores. Muchos de los trabajos ubican al FPGA, dadas sus características, como una herramienta que en un futuro podría ser la clave para implementación de transmisores totalmente digitales, como radio, televisión digital y SDR.

Dados los trabajos presentados, se concluye que el FPGA es una herramienta reconfigurable sobre la marcha que lo hace flexible, es de alta velocidad debido a su paralelismo, y de velocidad exacta, lo que lo hace ideal para realizar procesos de modulación, incluso sobre los PIC y DS-PIC<sup>2</sup> que no mantienen tasas altas de velocidad con la exactitud del FPGA. Además se ha encontrado que se tienen herramientas sencillas, como Simulink de Matlab, para programar un FPGA, superando a otros dispositivos.

$<sup>^2{\</sup>rm Microcontroladores}$  para el control de señales digitales

# Capítulo 3

# Desarrollo del Sistema

En este capítulo se presentan los fundamentos de cada una de las técnicas de modulación digital implementadas en este proyecto, conjuntamente con los resultados obtenidos de su implementación sobre el dispositivo FPGA. Se presenta también la descripción de los diferentes componentes del sistema de transmisión y recepción de datos.

# 3.1. Esquemas de Modulación Digital

Los esquemas de modulación digital estudiadas en este proyecto son: modulación por desplazamiento de amplitud - ASK, modulación por desplazamiento de frecuencia - FSK, modulación por desplazamiento de fase - PSK y la modulación de amplitud en cuadratura - QAM. A continuación se presenta brevemente los fundamentos de cada una de estas modulaciones.

## 3.1.1. Modulación por Desplazamiento de Amplitud

La modulación por desplazamiento de amplitud (ASK por sus siglas en inglés) consiste en variar la amplitud de la señal portadora en función de la señal moduladora, mientras que la frecuencia y la fase de la portadora permanecen constantes. Si la señal de información es multinivel (M bits por símbolo), entonces habrá M amplitudes posibles para la portadora [34]. La expresión general que describe la modulación ASK se presenta en la Ecuación 3.1.

$$S_i(t) = \sqrt{\frac{2E_i(t)}{T}}\cos(2\pi f_c t + \phi), \quad 0 \leqslant t \leqslant T, \ i = 1, \dots, M$$

(3.1)

Donde  $\phi$  corresponde a una fase arbitraria, T a la duración del símbolo,  $E_i$  a

la energía del símbolo *i*-ésimo. y  $f_c$  corresponde a la frecuencia de portadora. El ancho de banda BW de la modulación ASK se define por la Ecuación 3.2.

$$BW = \frac{f_b}{\log_2(M)} \tag{3.2}$$

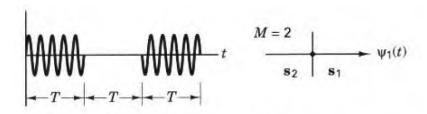

Donde  $f_b$  es la frecuencia de bit y M es la cantidad de estados de salida. En la Figura 3.1 se ilustra la modulación digital ASK en el dominio del tiempo.

Figura 3.1: Modulación digital ASK. Imagen tomada de [24].

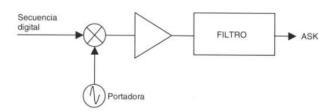

El esquema de generación de señales ASK consta en general de: un modulador que multiplica la portadora con el nivel de amplitud que representa la secuencia digital; un amplificador lineal y, un filtro para reducir el ruido. Este esquema se observa en la Figura 3.2.

Figura 3.2: Esquema de un modulador ASK. Imagen tomada de [34].

### 3.1.2. Modulación por Desplazamiento de Frecuencia

La modulación por desplazamiento de frecuencia (FSK por sus siglas en inglés) consiste en asignar una frecuencia distinta a cada uno de los símbolos de la fuente de información, manteniendo constante la amplitud y la fase [34] de la señal portadora. La señal de salida para una modulación FSK viene dada por la Ecuación 3.3, donde  $\phi$  es un valor de fase arbitrario, T es la duración del símbolo, E es la energía del símbolo y la frecuencia  $f_i$  puede tener M valores distintos. El ancho

de banda necesario para FSK es igual al necesario para ASK sumado al salto de frecuencia  $f_s$ , como se presenta en la Ecuación 3.4, donde  $f_b$  es la frecuencia de bit y M es la cantidad de estados de salida.

$$S_i(t) = \sqrt{\frac{2E(t)}{T}}\cos(2\pi f_i t + \phi), \quad 0 \leqslant t \leqslant T, \ i = 1, \dots, M$$

(3.3)

$$BW = \frac{f_b}{\log_2(M)} + f_s \tag{3.4}$$

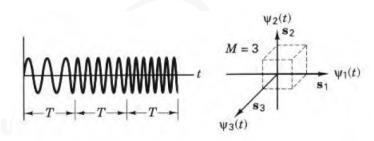

En la Figura 3.3 se puede observar un ejemplo de modulación digital FSK en el dominio del tiempo.

Figura 3.3: Modulación digital FSK. Imagen tomada de [24].

Para la generación de una señal FSK existen dos alternativas. La primera es un conmutador electrónico que selecciona uno de los M osciladores posibles en función del símbolo de entrada del modulador. Tiene el inconveniente de que la fase de la señal de salida no es constante en cada intervalo. La Figura 3.4 indica un generador de este tipo.

Figura 3.4: Generación de FSK mediante conmutador electrónico. *Imagen tomada de [34]*.

En el segundo método de generación se utiliza un oscilador de frecuencia variable, de esta forma se solventa el problema y se mantiene una fase constante

al cambio de símbolo. Para realizar el oscilador variable se utiliza una de las siguientes alternativas: Oscilador controlado por tensión (VCO - voltage controlled oscillator) o un circuito sintetizado mediante PLL. La Figura 3.5 muestra un esquema de este método.

Figura 3.5: Generación de FSK mediante oscilador de frecuencia variable. *Imagen tomada de [34]*.

Como se indicó en el Capítulo 1, en este trabajo se utiliza un demodulador basado en *GNU Radio* para comprobar el funcionamiento y medir el rendimiento del FPGA como base de los sitemas de modulación, el cual será estudiado en la Sección 3.4.2. Este software cuenta con un demodulador FSK gaussiano [9], que es una variación de FSK cuya implementación está limitada a la recepción de señales moduladas en 2-FSK.

#### 3.1.3. Modulación por Desplazamiento de Fase

La modulación por desplazamiento de fase (PSK por sus siglas en inglés) consiste en asignar una fase distinta a cada uno de los símbolos de la fuente de información, manteniendo constante la amplitud y la frecuencia. La señal de salida para una modulación PSK se define por la Ecuación 3.5.

$$S_i(t) = \sqrt{\frac{2E(t)}{T}}\cos(2\pi f_c t + \phi_i), \quad 0 \leqslant t \leqslant T, \ i = 1, \dots, M$$

(3.5)

Donde  $f_c$  es la frecuencia de portadora, T es la duración del símbolo, E es la energía del símbolo y la fase  $\phi_i$  puede tener M valores distintos.

Dada su naturaleza, sólo se puede utilizar en sistemas síncronos, puesto que no es posible detectar la fase mediante un sistema asíncrono. En la demodulación síncrona o coherente, el receptor debe disponer de un tono puro de la misma frecuencia y fase utilizadas en emisión, lo cual complica el diseño del circuito demodulador [34]. El ancho de banda necesario para PSK se define por la Ecuación 3.6, similar al de la modulación ASK, con la diferencia que en PSK toda la

potencia es utilizada para transmitir las bandas laterales, lo que la hace más robusta al ruido que ASK o FSK.

$$BW = \frac{f_b}{\log_2(M)} \tag{3.6}$$

Donde  $f_b$  es la frecuencia de bit y M es la cantidad de estados de salida. La Figura 3.6 es un ejemplo de modulación PSK.

Figura 3.6: Modulación digital PSK. Imagen tomada de [24].

El esquema 3.7 indica los bloques de un modulador PSK. El elemen

El esquema 3.7 indica los bloques de un modulador PSK. El elemento principal es un desplazador de fase.

Figura 3.7: Generación de PSK mediante oscilador de frecuencia variable. *Imagen tomada de [34]*.

En la Figura 3.8 se observa el diagrama vectorial o diagrama de constelación de una señal 4-PSK. Para decodificar un símbolo se debe identificar en qué sector de decisión se encuentra la representación vectorial de la señal obtenida por el receptor. Es así, que que cada símbolo tiene un intervalo de fases posibles.

Figura 3.8: Diagrama vectorial de una modulación 4-PSK. Imagen tomada de [34].

#### 3.1.4. Modulación de Amplitud en Cuadratura

En una modulación de amplitud en cuadratura (QAM por sus siglas en inglés) es posible usar conjuntamente modulación de amplitud y de fase [34]. La Figura 3.9 muestra un diagrama de bloques de un transmisor 16-QAM.

Figura 3.9: Diagrama transmisor 16-QAM. Imagen tomada de [29].

Cada símbolo para esta modulación tiene un tamaño de cuatro bits. Los datos binarios se dividen en cuatro canales: I, I', Q y Q'. Los valores I y Q determinan la polaridad en la salida en los convertidores de 2 a 4 niveles (1lógico = positivo y 0lógico = negativo). Los bits I' y Q' determinan la magnitud (1lógico = amplitudA y 0lógico = amplitudB). Por lo tanto para cada modulador de producto son posibles entonces diferentes cuatro salidas. Para el

modulador de producto I estas salidas son  $A sen(w_c t)$ ,  $-A sen(w_c t)$ ,  $B sen(w_c t)$  y  $-B sen(w_c t)$ . Para el modulador de producto Q son:  $A sen(w_c t)$ ,  $-A cos(w_c t)$ ,  $B cos(w_c t)$  y  $-B cos(w_c t)$ . El elemento sumador lineal combina las salidas de los moduladores de producto de canal y produce las 16 condiciones de salida necesarias para 16-QAM [29]. La Figura 3.10 indica un diagrama de fases y amplitudes de una señal 16-QAM.

Figura 3.10: Diagrama de constelación de 16-QAM.  $i_0$  e  $i_1$  indican el mapeo de amplitud en fase y  $q_0$  y  $q_1$  indican el mapeo de amplitud en cuadratura. *Imagen tomada de [11]*.

El ancho de banda mínimo necesario para 16-QAM viene dado por la Ecuación (3.7).

$$BW = \frac{f_b}{4} \tag{3.7}$$

Donde  $f_b$  es la frecuencia de bit.

#### 3.2. Desarrollo del Transmisor

Para la transmisión de datos utilizando esquemas de modulación digital se requiere que la información sea representada en un formato digital. Por lo tanto la necesidad de realizar la codificación de fuente, el cual es el proceso de asignar a cada mensaje de la fuente de información una palabra en código binario, lo que se conoce como codificación. Otro objetivo de la codificación es mapear el mensaje de origen en un código binario más compacto y luego realizar el proceso inverso [28]. La función del transmisor es tomar la información de una fuente de datos y adaptarla al canal de transmisión. Algunos parámetros fundamentales de un transmisor son la frecuencia de emisión, tipo de modulación, ancho de banda, potencia de emisión y ruido [34].

La frecuencia de emisión es la característica fundamental para el diseño de un transmisor, este depende del servicio y del canal o medio de transmisión. Se elige de acuerdo a normas dictadas por la Unión Internacional de Telecomunicaciones (UIT). El tipo de modulación depende de la complejidad de los equipos, ancho de banda, calidad y alcance requerido. La potencia de emisión condiciona el alcance de la señal a transmitir. Naturalmente, mientras mayor la potencia mayor será la zona de cobertura de una transmisión. Entre los componentes mas relevantes de un transmisor se encuentran: el oscilador el cual define la señal sinusoidal a una frecuencia fija, el modulador que se encarga de modificar las características de la señal portadora (frecuencia, fase o amplitud) dependiendo de la fuente de información y el amplificador de potencia o de radio frecuencia que eleva la potencia de salida con el fin de irradiar la señal mediante ondas electromagnética.

En un sistema de comunicaciones, el canal corresponde al medio por el cual se transmite la información. Este medio puede ser de tipo radioeléctrico (atmosférico, vacío) o físico (cables, guía de ondas, fibra óptica). Para transmitir la señal de radiofrecuencia de forma inalámbrica se usa una antena, que permite específicamente radiar o recibir ondas electromagnéticas. Algunos parámetros a considerar en una antena son su impedancia, directividad, ancho de banda, eficiencia, ganancia y su diagrama de radiación, como se puede revisar en detalle en [17].

Con el objetivo de detectar y corregir errores producidos en el canal de comunicación se realiza lo que se denomina codificación del canal. Estos errores son

consecuencia del ruido y la distorsión introducidos tanto por el medio de propagación como por las no linealidades del propio sistema de comunicaciones. El codificador de canal tiene como entrada una señal digital procedente del codificador de fuente [31]. Cabe recalcar que en el sistema de transmisión diseñado en este proyecto no se incorpora procesos de codificación de fuente ni codificación de canal puesto que se centra en la evaluación de diferentes técnicas de modulación exclusivamente, dejando abierta la oportunidad de implementar estos procesos en el futuro.

El esquema general del transmisor planteado en este proyecto se observa en la Figura 1.1. Las distintas técnicas de modulación implementadas se sustentan en el uso de en un dispositivo programable FPGA (Field Programmable Gate Array), concretamente haciendo uso de la plataforma Spartan 3E Starter de Xilinx<sup>1</sup>. La información a transmitir es una secuencia de bits almacenada en la memoria interna del FPGA. En las siguientes secciones se describe cada uno de los bloques utilizados para la transmisión.

# 3.2.1. Field Programmable Gate Array

Un FPGA (Field Programmable Gate Array) es un dispositivo semiconductor que se fundamenta en el uso de una matriz de bloques lógicos configurables (CLB - Configurable Logic Blocks) conectados a través de interconexiones programables mediante código desarrollado por el usuario [2].

#### Spartan 3E Starter Kit

Constituye una tarjeta de desarrollo basada en el dispositivo FPGA XC3S500E-FG320 Spartan-3E de Xilinx. Algunas de sus características principales denotan que contiene 500000 compuertas, lo que es equivalente a más de 10000 celdas lógicas, 232 pines de Entrada/Salida, tiene una memoria flash paralela de 16 MBytes, memoria DDR SDRAM de 64 MBytes accesible a una velocidad mayor a 100 MHZ y 16 Mbits de memoria flash accesibles mediante un interfaz SPI. Cuenta además con un oscilador de 50 MHz y posee un módulo conversor digital—analógico (DAC) de cuatro canales y un conector de expansión de 100 pines Hirose FX2², cuatro pulsantes y cuatro interruptores, luces LED y pantalla de cristal líquido LCD de dos líneas y 16 caracteres. En la Figura 3.11 se puede

<sup>&</sup>lt;sup>1</sup>Página web del fabricante: http://www.xilinx.com/

<sup>&</sup>lt;sup>2</sup>Página web del fabricante: https://www.hirose.com/product/en/products/FX2

observar la tarjeta de desarrollo SPARTAN 3E [32].

La programación de este FPGA se desarrolla en el software Xilinx ISE (Integrated Synthesis Environment) el cual proporciona herramientas para el análisis y compilación de códigos de programación. Mediante este software se puede realizar procesos de simulación con ISIM³ (simulador de lógica) para la verificación del comportamiento de un programa determinado.

Figura 3.11: Spartan 3E starter kit de Xilinx.

El lenguaje de programación usado es VHSIC Hardware Description Language (VHDL), el cual está definido por la IEEE (Institute of Electrical and Electronics Engineers) en el estándar STD 1076 [18] y cuyo lenguaje es usado para describir el comportamiento de circuitos digitales, principalmente para programar FPGA (Field Programmable Gate Array), ASIC (Circuito Integrado para Aplicaciones Específicas), y PLD (Dispositivos Lógicos Programables).

<sup>&</sup>lt;sup>3</sup>Página web del software: https://www.xilinx.com/products/design-tools/isim.html

#### 3.2.2. Conversor Digital-Analógico - DAC

Un DAC (Digital to Analog Converter) realiza la conversión Digital-Analógica que corresponde al proceso de tomar un valor representado en código digital (como binario o BCD) y convertirlo en un voltaje o corriente de salida que sea proporcional al valor numérico de entrada [27].

La plataforma Spartan 3E Starter Kit incluye un conversor Digital-Analógico de cuatro canales que utiliza el protocolo de comunicación SPI (Serial Peripheral Interface). El dispositivo es un DAC LTC2624<sup>4</sup> el cual tiene una resolución de 12 bits sin signo. En el interior del convertidor D/A la interfaz SPI está formado por un registro de desplazamiento de 32 bits. Cada palabra de comando de 32 bits consiste en un comando de 4 bits, la dirección del DAC(A, B, C o D) de 4 bits y los 12 bits del dato a convertir, el resto de bits no son usados [13]. La velocidad de datos a la salida del conversor Digital-Analógico se ve directamente relacionada con la cantidad de bits que se necesitan enviar mediante el protocolo de comunicación SPI. La plataforma del Spartan 3E consta con un reloj de 50 MHz, conocido comúnmente simplemente como clock que determina la máxima velocidad de conversión entre el DAC y el FPGA. La siguiente expresión determina la máxima velocidad de conversión par este DAC.

$$Velocidad Conversion = \frac{Clock}{bits SPI}$$

$$Velocidad Conversion = \frac{50MHz}{32}$$

(3.8)

Velocidad Conversion = 1562500 palabras/seg

Para obtener una señal sinusoidal a la salida del DAC, misma que se utilizará posteriormente en los procesos de modulación digital, se realiza la reconstrucción de una señal seno a partir de un número determinado de sus muestras. Suponiendo una señal discreta de tipo seno, se defina mediante 24 muestras, la frecuencia máxima de dicha señal después de la conversión Digital/Analógica puede obtenerse mediante la Ecuación 3.9:

$$FrecuenciaSeno = \frac{VelocidadConversion}{\#muestrasSeno}$$

(3.9)

<sup>&</sup>lt;sup>4</sup>Página web del fabricante: http://www.linear.com/

$$FrecuenciaSeno = \frac{1562500}{24}$$

$$FrecuenciaSeno = 65104,1 \text{ Hz}$$

Debido a esta limitación del interfaz de comunicaciones SPI del DAC, no se puede obtener una salida analógica de mayores velocidades de oscilación, lo que resulta una limitante para el despliegue de sistemas digitales de comunicaciones basados enteramente en los componentes intrínsecos de la tarjeta Spartan 3E Starter Kit. La señal resultante de la conversión no lograría alcanzar la frecuencia de radio frecuencia que se necesita para la transmisión de datos mediante el espectro electromagnético, por lo tanto el DAC LTC2624 integrado en la tarjeta Spartan 3E Starter Kit no es utilizado en el desarrollo de este proyeto.

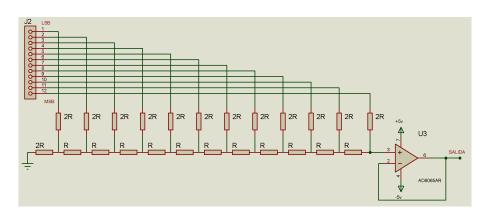

Para solucionar esta limitación se opta por la inclusión de un conversor de mayor velocidad. Una forma simple y económica de implementar un DAC manteniendo la resolución de 12 bits pero con alta velocidad de conversión es mediante una clásica red de conversión basada en el acople de resistencias del tipo R-2R. En esta red de tipo escalera, las resistencias guardan una relación de 2 a 1 [27]. La Figura 3.12 muestra el diagrama correspondiente a un DAC de este tipo.

Figura 3.12: DAC R-2R. Figura tomada de Proteus 8.0

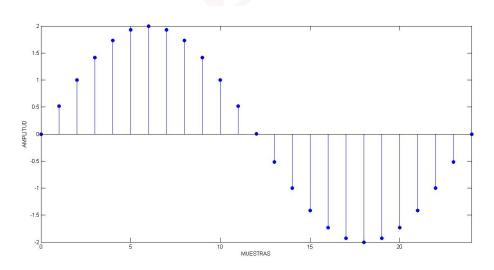

La velocidad de este circuito depende fundamentalmente de la velocidad de entrada de datos. Si la señal discreta de tipo seno tiene 24 muestras, como se muestra en la Figura 3.13, y cada muestra es enviada a este tipo de DAC a la velocidad máxima de reloj del FPGA (50Mhz), se tiene que la señal sintética resultante puede reconstruirse a una frecuencia  $f_c = 50 \, MHz/24 = 2,08 \, MHz$ . La frecuencia de esta señal sinusoidal depende directamente de la tasa de muestreo y el número de muestras de la señal discreta seno almacenada en memoria.

El número de bits en la entrada del DAC define la resolución del conversor y el tamaño de paso de voltaje del DAC. El tamaño de paso es una relación entre la salida analógica de voltaje y el valor de entrada digital descrito por la Ecuación 3.10.

$$TamanoPaso = \frac{VoltajeSalida}{EntradaDigital}$$

(3.10)

$${\rm TamanoPaso} = \frac{3{,}3V}{2^{12}-1}$$

TamanoPaso = 805,86 vV

Figura 3.13: Señal tipo seno muestreada.

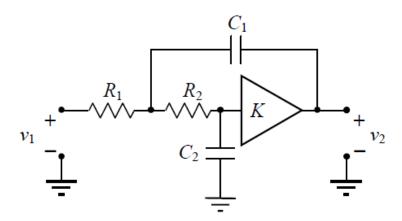

Con el fin de eliminar el ruido de cuantización de la señal sinusoidal en la salida del DAC se incorpora un filtro pasa-bajos activo en la salida. Un filtro pasa-bajos (LPF Low pass filter) permite el paso de las frecuencias menores a cierta frecuencia  $f_c$  denominada de corte y bloquea las mayores a dicha frecuenca de corte [15].

Para el diseño se considera el filtro con realimentación positiva pasabajos propuesta por Sallen y Key [15], ilustrada en la Figura 3.14, el cual consta de dos resistencias, dos capacitores y un amplificador operacional no inversor.

Figura 3.14: Filtro pasabajos de segundo orden Sallen y Key.  $Imagen\ tomada\ de\ [15].$

La frecuencia de corte del filtro se define según la Ecuación 3.11

$$f_c = \frac{1}{2 * \pi * \sqrt{R_1 R_2 C_1 C_2}} \tag{3.11}$$

Para realizar el filtro se utiliza el amplificador operacional de alto rendimiento AD8065<sup>5</sup> que tiene una velocidad de 145MHz. Este componente es comúnmente utilizado en instrumentación, filtros y controladores de conversores Digital-Analógico. La característica principal por la que se elige este amplificador operacional en el contexto de este proyecto, es el parámetro del tiempo de establecimiento (Settling Time) del amplificador, que se encuentra entre 55 y 205 nanosegundos, este es el tiempo transcurrido desde la aplicación de una entrada escalón hasta que se estabilice este valor en la salida [3].

# 3.2.3. Amplificación de Radiofrecuencia RF

Con el objetivo de irradiar la señal y tener mayor alcance de transmisión se utiliza un amplificador RF. Específicamente se ha incorporado al sistema transmisor un dispositivo AC557 <sup>6</sup> de *Teledyne Cougar*, que corresponde a un amplificador de radiofrecuencia con bajo ruido el cual tiene una ganancia de 15dB, trabaja en el rango de frecuencia de 0.3 a 500 MHz y tiene una Figura de ruido de 4dB. Los conectores de entrada y salida son de tipo SMA con una impedancia de 50 Ohms [26].

<sup>&</sup>lt;sup>5</sup>Página web del fabricante: http://www.analog.com/

<sup>&</sup>lt;sup>6</sup>Página web del fabricante: http://www.teledyne-cougar.com/

# 3.3. Implementación de Modulaciones Digitales en FPGA

En esta sección se documenta la implementación de los distintos tipos de modulaciones digitales. Es importante denotar, que todas las técnicas implementadas requieren de una señal portadora, la que se implementó a manera de un componente reutilizable que puede ser integrado a cualquier esquema de modulación programado dentro del FPGA.

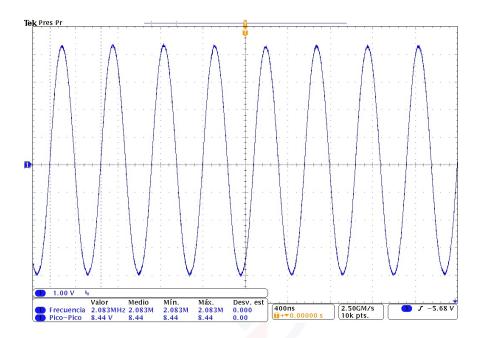

#### 3.3.1. Generación de portadora

El sistema transmisor está diseñado para para la banda MF (frecuencia media) el cual ocupa el rango de frecuencias de 300KHz a 3MHz. Para generar la señal portadora se almacena en la memoria del FPGA un vector de datos que contiene 24 valores resultantes del muestreo de un ciclo de una señal sinusoidal del tipo  $y(x) = A \cdot \sin{(x+\phi)}$ , los valores discretos de esta señal tienen un tamaño de 12 bits, esto es 4096 valores posibles. Así, la frecuencia de la portadora puede estimarse a partir del número de muestras de la señal seno almacenada y que se utilicen por unidad de tiempo para la reconstrucción de la misma. Este número de muestras corresponde a la frecuencia de muestreo de la señal almacenada.

$$Frecuencia Seno = \frac{Frecuencia De Muestreo}{\# Muestras Seno}$$

(3.12)

La velocidad máxima de muestreo es igual a la velocidad del reloj utilizado por el FPGA, en este caso 50 MHz. Con el fin de no interferir con las señales de radiodifusión por Amplitud Modulada comercial se elige una frecuencia mayor a la banda asignada para este tipo de transmisión (535 a 1605 KHz) [29], por lo tanto con la señal sinusoidal de 24 muestras se obtiene una señal portadora cuya frecuencia está dada por las siguientes expresiones:

Frecuencia Seno =

$$\frac{50000000}{24} = 2,083 MHz$$

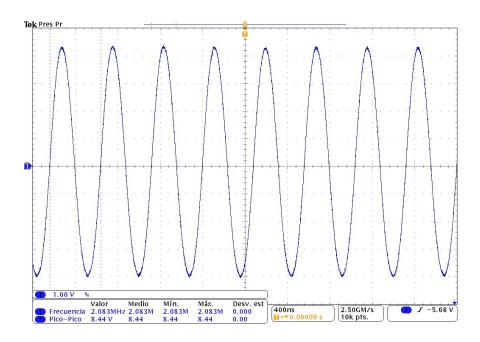

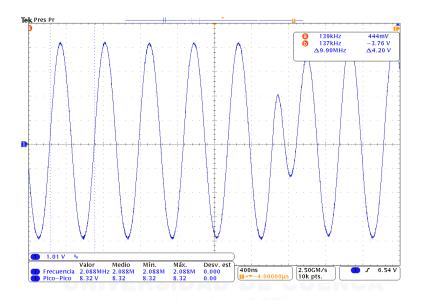

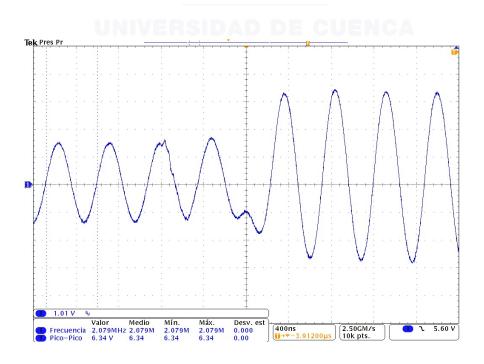

Por lo tanto, cada valor discreto de la función seno se transmite de forma paralela a la red DAC R-2R con una velocidad de 50MHz obteniendo a la salida una señal tipo seno con una frecuencia de oscilación de 2.083 MHz. En la Figura 3.15 se observa la señal a la salida del DAC R-2R capturada con un osciloscopio.

Figura 3.15: Señal sinusoidal generada con el FPGA.

# 3.3.2. Modulación 2-ASK

La generación de una señal ASK con moduladora binaria es equivalente a conectar y desconectar la señal portadora, por lo que recibe el nombre de OOK (*On-Off Keying*). Para implementar esta modulación en el FPGA basta con multiplicar la señal portadora con el bit a enviar (0 o 1).

$$ASK = portadora(t) \cdot simbolo(n)$$

(3.13)

La frecuencia de símbolo (Baudios) se controla mediante un contador de espera y depende del reloj interno del FPGA. Realizando 500 conteos de espera, mediante el uso de una variable dentro del FPGA durante el cual no se realiza un cambio de símbolo, se tiene:

$$f_s = \frac{Clock}{\# \text{ de Conteos}}$$

$$f_s = \frac{50000000}{500}$$

$$f_s = 100000 Baudios$$

(3.14)

Debido a que en la modulación 2-ASK cada símbolo tiene un solo bit, la frecuencia de símbolo es igual a la frecuencia de bit,  $f_b = 100 \; Kbps$ . El ancho de

banda de esta modulación viene dado por la Ecuación (3.2), como se muestra a continuación:

$$BW = \frac{100000}{\log_2(2)}$$

$$BW = 100 \, KHz$$

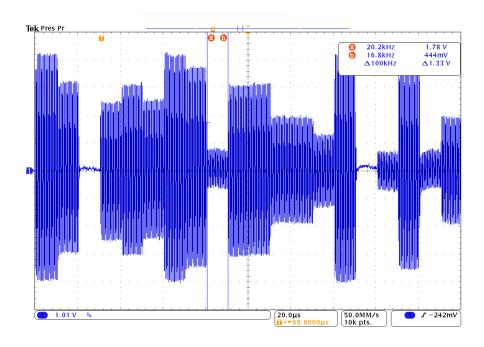

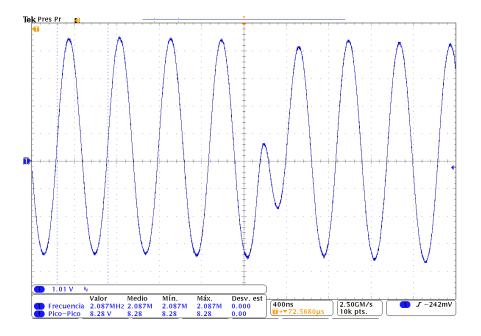

En la Figura 3.16 se presenta la señal modulada obtenida a la salida del DAC. Aquí se puede observar, que la frecuencia de símbolo es 100KHz. En la Figura 3.17 se muestra la señal modulada en en el dominio de la frecuencia, utilizando la función FFT del osciloscopio donde se aprecia el ancho de banda de 100KHz para 2-ASK.

Figura 3.16: Señal modulada 2-ASK.

Figura 3.17: Señal modulada 2-ASK en el dominio de la frecuencia.

# 3.3.3. Modulación 4-ASK

Para este esquema de modulación digital se generan cuatro diferentes amplitudes de la señal portadora portadora, considerando que cada símbolo a enviar se representa mediante de dos bits. Para realizar el proceso de modulación, se multiplica la señal portadora con el equivalente decimal de cada símbolo a enviar, como se indica en la Tabla 3.1.

| Símbolo | Decimal |  |  |

|---------|---------|--|--|

| 00      | 0       |  |  |

| 01      | 1       |  |  |

| 10      | 2       |  |  |

| 11      | 3       |  |  |

Tabla 3.1: Equivalencia binario-decimal

Para valor de frecuencia de símbolo se utiliza el mismo valor que el empleado en 2-ASK, específicamente,  $f_s = 100000 \; Baudios$ , y la frecuencia de bit depende del número de bits (n) que componen cada símbolo.

$$f_b = n \cdot f_s \tag{3.15}$$

$$f_b = 2 \cdot 100000$$

$$f_b = 200Kbps$$

En este contexto, el ancho de banda se define por la Ecuación (3.4), de la siguiente manera:

$$BW = \frac{200000}{\log_2 4}$$

$$BW = 100 \ KHz$$

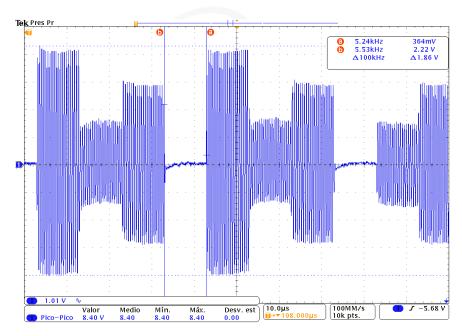

El resultado de la modulación se observa en la Figura 3.18, donde se muestra la frecuencia de símbolo de 100KHz. La Figura 3.19 muestra la señal modulada en el dominio de la frecuencia, donde se puede identificar un ancho de banda de 100KHz.

Figura 3.18: Señal modulada 4-ASK.

Figura 3.19: Señal modulada 4-ASK en el dominio de la frecuencia.

#### 3.3.4. Modulación 8-ASK

El proceso de generación de la señal 8-ASK es similar a 2-ASK y 4-ASK, presentadas en las secciones 3.3.2 y 3.3.3. Para el caso particular de 8-ASK, cada símbolo se representa mediante 3 bits por lo que la señal modulada tendrá 8 amplitudes diferentes, como se indica en la Tabla 3.2.

| Símbolo | Decimal |

|---------|---------|

| 000     | 0       |

| 001     | 1       |

| 010     | 2       |

| 011     | 3       |

| 100     | 4       |

| 101     | 5       |

| 110     | 6       |

| 111     | 7       |

Tabla 3.2: equivalencia binario-decimal en 8-ASK

La frecuencia de símbolo correspondiente es  $f_s = 100000 \ Baudios$ , y la frecuencia de bit viene dado por:

$$f_b = n \cdot f_s \tag{3.16}$$

$$f_b = 3 \cdot 100000$$

$$f_b = 300 Kbps$$

Donde n es el número de bits que componen cada símbolo. Y el ancho de banda viene dado por la Ecuación (3.4).

$$BW = \frac{300000}{log_2 8}$$

$$BW = 100 \ KHz$$

El resultado de la modulación en el dominio del tiempo se observa en la Figura 3.20, mientra que la Figura 3.21 muestra el espectro de frecuencias de la señal.

Figura 3.20: Señal modulada 8-ASK.

Figura 3.21: Señal modulada 8-ASK en el dominio de la frecuencia.

#### 3.3.5. Modulación 2-FSK

Para generar una señal 2-FSK en el FPGA se utiliza el método de conmutador electrónico explicado en la Sección 3.1.2. Esta modulación consta de dos estados por lo tanto se necesita un igual número de frecuencias para transmitir la señal. La primera frecuencia  $f_1$  es la señal portadora a 2.08 MHz que se logra con 24 muestras de unas señal seno. La segunda frecuencia se obtiene con una señal seno de 25 muestras con lo que se obtiene:

Frecuencia Seno =

$$\frac{\text{Frecuencia De Muestreo}}{\# muestras Seno}$$

(3.17)

Frecuencia Seno =  $\frac{50000000}{25} = 2 MHz$

El símbolo tiene un solo bit por lo que dependiendo si este es 0 o 1 se elegirá uno de los osciladores. La frecuencia de símbolo se establece como  $f_s = 100000 \ Baudios$ . Dado que 2-FSK es una modulación binaria la frecuencia de símbolo es la misma que la frecuencia de bit  $f_b$ . El ancho de banda viene dado por la Ecuación (3.4) y es:

$$BW = \frac{300000}{\log_2(8)} + (2,083 \times 10^6 - 2 \times 10^6)$$

#### $BW = 183,3 \ KHz$

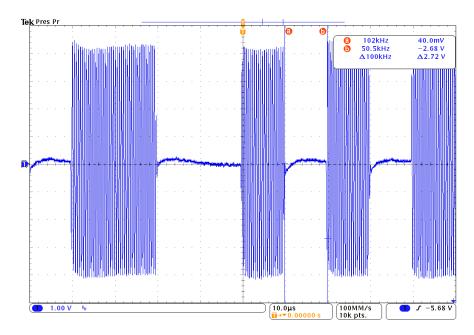

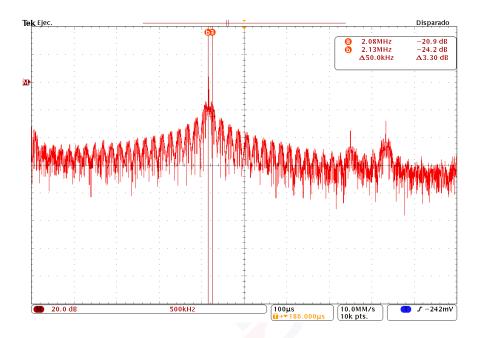

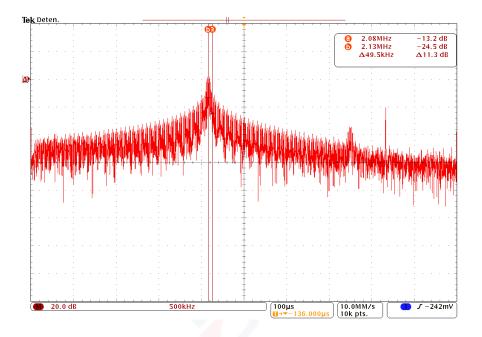

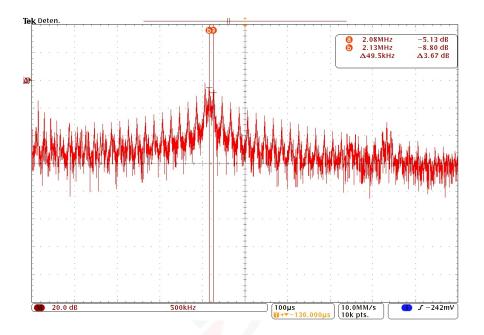

La Figura 3.22 muestra la señal modulada obtenida en el dominio del tiempo, mientras que el espectro de frecuencias de la modulación se presenta en la Figura 3.23.

Figura 3.22: Señal modulada 2-FSK.

Figura 3.23: Señal modulada 2-FSK en el dominio de la frecuencia.

#### 3.3.6. Modulación 2-PSK

Para la generación de una señal 2-PSK se necesita de dos señales desfasadas, la primera con 0 grados de desfase y la segunda con 180 grados. La función seno portadora representa un desfase de 0 grados y para la segunda señal se realiza el muestreo de una señal sinusoidal con desfase 180 grados. Por lo tanto, dependiendo del símbolo a enviar (0 o 1) se escoge entre una de las dos señales seno.

La frecuencia de símbolo se establece como  $f_s = 100000 \, Baudios$ . Dado que 2-PSK corresponde a una modulación binaria la frecuencia de símbolo es la misma que la frecuencia de bit,  $f_b$ . El ancho de banda de esta modulación viene dado por la Ecuación(3.6):

$$BW = \frac{100000}{\log_2(2)}$$

$$BW = 100 \ KHz$$

En la Figura 3.24 se puede observar la señal modulada además de un cambio de fase. En la Figura 3.25 se puede vizualizar el espectro de frecuencias de la modulación 2-PSK.

Figura 3.24: Señal modulada 2-PSK.

Figura 3.25: Señal modulada 2-PSK en el dominio de la frecuencia.

#### UNIVERSIDAD DE CUENCA

## 3.3.7. Modulación 4-PSK

Para generar una modulación 4-PSK también conocida como QPSK (Modulación por cambio de frecuencias ortogonales), se necesita de cuatro señales desfasadas. Las fases necesarias son: 0, 90, 180 y 270 grados. Para tener cada señal se construye cuatro funciones seno con las fases indicadas anteriormente mediante las 24 muestras almacenadas en memoria y con el fin de lograr una frecuencia de portadora de 2,08 MHz. Cada símbolo se representa mediante dos bits por lo tanto es posible construir cuatro símbolos diferentes. Dependiendo del símbolo a enviar se selecciona una entre las cuatro señales sinusoidales disponibles con diferentes fases. Se elige una frecuencia de símbolo de  $f_s = 100000$  Baudios, la frecuencia de bit es:

$$f_b = n \cdot f_s$$

(3.18)

$f_b = 2 \cdot 100000 = 200 \text{Kbps}$

El ancho de banda necesario para transmitir la señal viene dado por la Ecuación (3.6) y es:

$$BW = \frac{200000}{\log_2(4)}$$

#### $BW = 100 \ KHz$

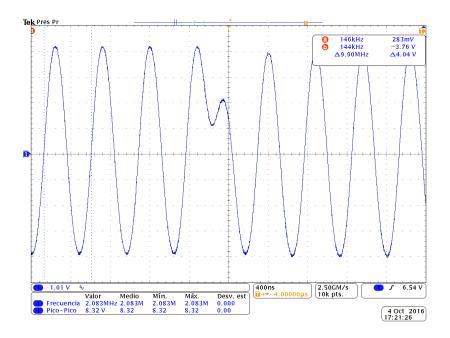

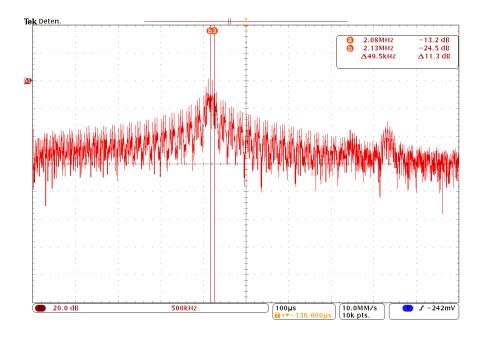

En la Figura 3.26 se puede observar la señal a la salida del modulador. Se evidencia un cambio de fase de 270 grados. La Figura 3.27 muestra la señal modulada en el dominio de la frecuencia.

Figura 3.26: Señal modulada 4-PSK .

Figura 3.27: Señal modulada 4-PSK en el dominio de la frecuencia.

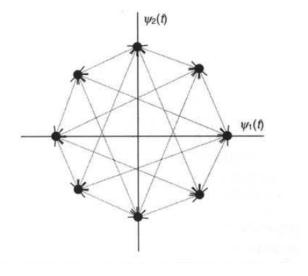

El diagrama de fase para 4-PSK tiene cuatro sectores de decisión, esto se observa en la Figura 3.28, que muestra el diagrama de constelación de esta técnica de modulación.

Figura 3.28: Diagrama de constelación 4-PSK.

#### 3.3.8. Modulación 8-PSK

El proceso de generación de una señal 8-PSK se fundamenta en los mismos que aquellos utilizados para la modulación 4-PSK, con la diferencia que ahora se necesitan ocho diferentes fases, específicamente: 0, 45, 90, 135, 180, 225, 270, y 315 grados. Para esta modulación, cada símbolo se representa mediante el uso de tres bits por lo que es posible disponer de 8 valores diferentes. Dependiendo del símbolo a enviar se selecciona entre una de las ocho funciones generadas. Se define una frecuencia de símbolo de  $f_s = 100000$  Baudios, y por tanto la frecuencia de bit según la Ecuación 3.19 es:

$$f_b = n \cdot f_s \tag{3.19}$$

$$f_b = 3 \cdot 100000$$

$$f_b = 300Kbps$$

El ancho de banda mínimo necesario de esta modulación viene dado por la Ecuación 3.6 y es:

$$BW = \frac{300000}{\log_2(8)}$$

$$BW = 100 \ KHz$$

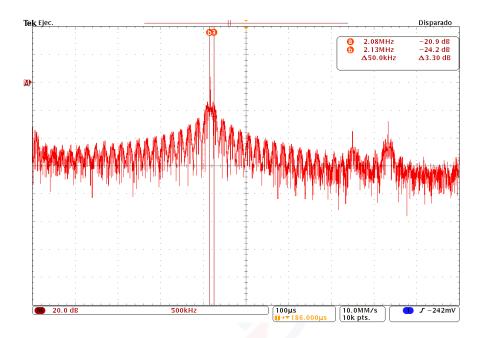

Figura 3.29: Señal modulada 8-PSK .

En la Figura 3.29 se puede observar la señal a la salida del modulador representada en el dominio del tiempo. La Figura 3.31 muestra la señal modulada en el dominio de la frecuencia. El diagrama de fase para 8-PSK tiene ocho sectores de decisión, esto se observa en la Figura 3.30.

Figura 3.30: Diagrama de constelación 8-PSK.

Figura 3.31: Señal modulada 8-PSK en el dominio de la frecuencia.

#### 3.3.9. Modulación 16-QAM

La implementación de la técnica de modulación 16-QAM se basa en el esquema mostrado en la Figura 3.9. La señal  $sen(\omega_c t)$  corresponde a la señal portadora generada según se mencionó en la Sección 3.3.1, mientras que la señal  $cos(\omega_c t)$  corresponde a la misma señal portadora pero desfasada 90 grados. La Tabla 3.3 muestra los valores a la salida del convertidor de 2 a 4 niveles para el canal I y la Tabla 3.4 para el canal Q.

| Ι | I' | Salida |

|---|----|--------|

| 0 | 0  | 3V     |

| 0 | 1  | 1V     |

| 1 | 0  | -1V    |

| 1 | 1  | -3V    |

Tabla 3.3: Tabla de verdad convertidor canal I

| Q | Q, | Salida |

|---|----|--------|

| 0 | 0  | 3V     |

| 0 | 1  | 1V     |

| 1 | 0  | -1V    |

| 1 | 1  | -3V    |

Tabla 3.4: Tabla de verdad convertidor canal Q

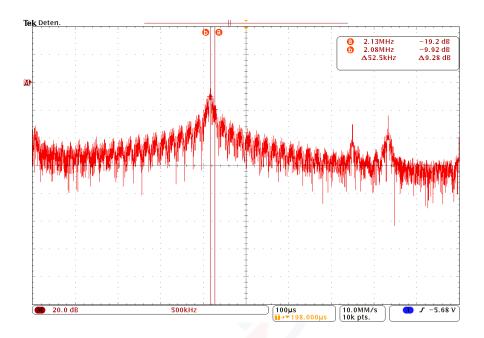

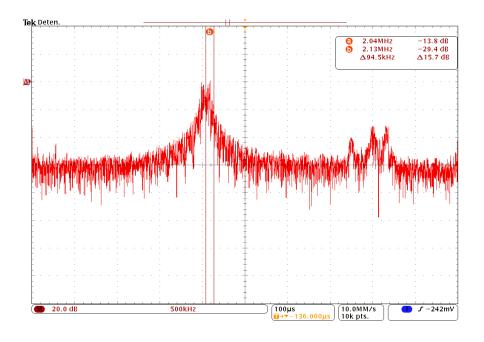

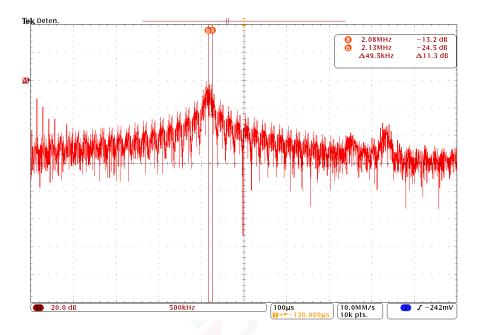

Una vez determinados los coeficientes de las componentes I y Q para los cuatro niveles de amplitud necesarios, estos son utilizados para establecer la amplitud de las señales seno y coseno respectivamente. Posteriormente, se suman las dos señales obteniendo la modulación 16-QAM. La Figura 3.32 presenta la señal modulada a la salida del convertidor digital-analógico en el dominio del tiempo, donde se puede observar un cambio de amplitud y fase. En la Figura 3.33 muestra la señal modulada en el dominio de la frecuencia.

Para esta modulación, la frecuencia de bit es  $f_b = 100 \, KHz$ , además el ancho de banda de la modulación viene dado por la Ecuación (3.7) y es:

$$BW = \frac{100000}{4}$$

$$BW = 25 \text{ KHz}$$

Figura 3.32: Señal modulada 16-QAM.

Figura 3.33: Espectro de frecuencias de modulación 16-QAM.

Las potencia de salida de cada señal modulada depende del tipo de modulación y del amplificador de radio frecuencia. La Tabla 3.5 indica los diferentes valores de potencia a la salida del transmisor, antes de ingresar a la antena, medidas haciendo uso de un osciloscopio.

| Tipo de modulación | Potencia   |

|--------------------|------------|

| 2-ASK              | -9.92 dBm  |

| 4-ASK              | -20.29 dBm |

| 8-ASK              | -20.9 dBm  |

| 2-PSK              | -13.2 dBm  |

| 4-PSK              | -13.2 dBm  |

| 8-PSK              | -13.2 dBm  |

| 2-FSK              | -13.8 dBm  |

| 16-QAM             | -5.13 dBm  |

Tabla 3.5: Potencias de salida del amplificador de radio frecuencia.

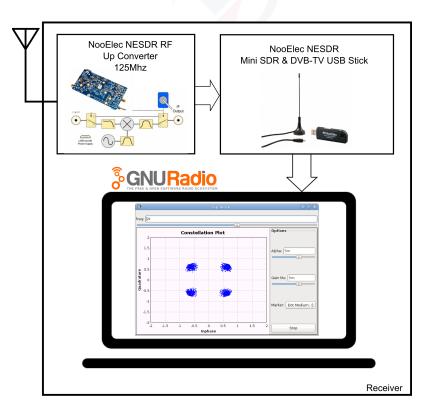

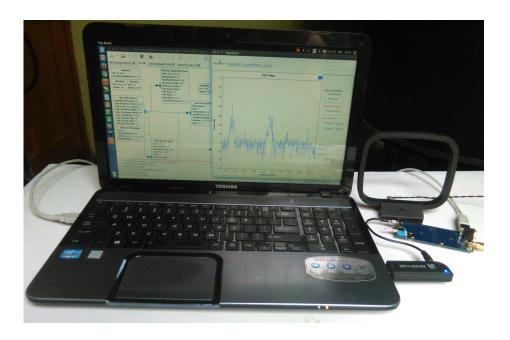

# 3.4. Desarrollo del Receptor

En este proyecto, el equipo receptor tiene como finalidad ser el elemento de validación del desarrollo del equipo transmisor implementado. Su diagrama general se muestra en la Figura 3.34. Como se observa en la Figura 3.34, existen

tres componentes principales que integran el sistema de recepción de señales: un circuito elevador de frecuencia o en inglés *Up converter*, un receptor de radio definido por software (SDR por sus siglas en inglés) para televisión y radio digital con conexión USB y finalmente, el software GNU Radio. Cada uno cumple con un propósito específico dentro del equipo receptor que será presentado en las subsecciones siguientes.

#### 3.4.1. Implementación del Sistema de Recepción

En esta sección se introducen y presentan detalles técnicos relacionados a los componentes utilizados en el receptor, mostrado en la Figura 3.34, enfocando principalmente, las características que los hacen propicios para su uso dentro de este proyecto.

Figura 3.34: Sistema receptor basado en GNU Radio.

#### Circuito Elevador de Frecuencia

El componente elevador de frecuencia corresponde a un dispositivo con una entrada y una salida cuya función es elevar la frecuencia del puerto entrada en un valor definido y colocar la señal a mayor frecuencia en el puerto de salida. En este

proyecto, este dispositivo se utiliza para realizar un desplazamiento en frecuencia de una señal determinada, con el objetivo de ubicarla a más alta frecuencia y así, conseguir que una señal de baja frecuencia pueda ser recibida por un equipo diseñado para recibir señales de más alta frecuencia. El circuito elevador de frecuencia utilizado en el receptor pertenece al fabricante NooElec<sup>7</sup>. Este dispositivo puede funcionar en dos diferentes modos: upconverter, que eleva la frecuencia 125 Mhz sobre la señal del puerto de entrada y la envía al puerto de salida, y en modo passtrought que permite el paso directo de la señal del puerto de entrada hacia el puerto de salida. Este dispositivo permite una señal de entrada desde 0,1MHz hasta 60Mhz con una potencia máxima de +1dBm y un oscilador local de +7dBm. Este dispositivo cuenta con conectores SMA de 50 ohm en sus puertos de entrada y salida [16].

#### Receptor SDR para televisión y radio digital con conexión USB

Este dispositivo comercial, corresponde a un equipo de uso doméstico y de bajo costo utilizado normalmente para la recepción y sintonización de radio y televisión digital en un computador personal, específicamente, basada en la incorporación de un componente SDR. El receptor SDR utilizado es el RTL-SDR  $2832U^8$  que cuenta con el circuito integrado RTL2832U fabricado por  $Realtek^9$ , el mismo que puede configurarse para la recibir señales transmitidas mediante multiplexación por división de frecuencia ortogonal codificada (COFDM) y además, el circuito integrado R820T fabricado por  $Rafael\ Electronics\ INC^{10}$  enfocado en la sintonización de frecuencias. Este dispositivo cuenta con una conexión USB para realizar la comunicación con un computadora. Este receptor SDR soporta un rango de frecuencias desde 24MHz a 1766Mhz, frecuencia de muestreo en banda base de hasta de hasta 3.8MHz, aunque es recomendable para no tener muestras eliminadas, frecuencias de muestreo de hasta 2.4MHz. Además, el dispositivo facilita el uso de una variable de ganancia de radio frecuencia configurable de acuerdo a la Tabla 3.6 [22]. La lista de valores de ganancia configurables para cualquier dispositivo receptor SDR puede ser obtenida al realizar el comando rtl-sdr -t dentro de la consola del sistema operativo del computador al que se encuentre conectado el dispositivo receptor SDR.

<sup>&</sup>lt;sup>7</sup>NooElec, página web: http://www.nooelec.com

<sup>&</sup>lt;sup>8</sup>Fabricante: RTL-SDR. Sitio web: http://www.rtl-sdr.com/

<sup>&</sup>lt;sup>9</sup>Realtek, sitio web: http://www.realtek.com.tw/

<sup>&</sup>lt;sup>10</sup>Rafael Electronics, sitio web: http://www.rafaelmicro.com/

Como una característica importante, se debe mencionar que este dispositivo soporta la recepción de diferentes señales de transmisión de radio y televisión comerciales, entre las que se destacan: Difusión Digital de Audio DAB que es un estándar para la transmisión de audio digital, cuya definición y estándares se encuentran en [6], Difusión Digital de Video Terrestre DVB-T que es un estándar para la transmisión de televisión, cuya definición y estándares se encuentran en [7] y finalmente frecuencia modulada FM. Además, el dispositivo provee la flexibilidad de recibir señales experimentales a nivel de estudio y desarrollo.

Tabla 3.6: Valores de Ganancias Configurables para el Receptor SDR.

| Ganancias [dB] |      |            |      |             |      |     |      |

|----------------|------|------------|------|-------------|------|-----|------|

| G1             | 0.0  | <b>G</b> 9 | 14.4 | G17         | 29.7 | G25 | 43.4 |

| $\mathbf{G2}$  | 0.9  | G10        | 15.7 | G18         | 32.8 | G26 | 43.9 |

| $\mathbf{G3}$  | 1.4  | G11        | 16.6 | <b>G1</b> 9 | 33.8 | G27 | 44.5 |

| G4             | 2.7  | G12        | 19.7 | G20         | 36.4 | G28 | 48.0 |

| G5             | 3.7  | G13        | 20.7 | <b>G21</b>  | 37.2 | G29 | 49.6 |

| G6             | 7.7  | G14        | 22.9 | G22         | 38.6 |     |      |

| <b>G7</b>      | 8.7  | G15        | 25.4 | G23         | 40.2 | HEN | CA.  |

| <b>G8</b>      | 12.5 | G16        | 28.0 | <b>G24</b>  | 42.1 |     |      |

Dado que este dispositivo soporta el rango de frecuencias anteriormente mencionadas y el hecho que la señal que se transmitirá tiene una frecuencia de portadora de 2,083MHz, se justifica el uso del circuito *upconverter* para ubicar la frecuencia recibida en 127,083 MHz permitida por el receptor utilizado.

#### 3.4.2. Software GNU Radio

Textualmente en [20] se indica que "GNU Radio es un software de desarrollo de herramientas de código libre y abierto que proporciona bloques de procesamiento de señales para implementar software radio. Este programa es ampliamente utilizado en entornos de aficionados, académicos y comercial, contribuyendo tanto en la investigación de comunicaciones inalámbricas, así como en la implementación de sistemas de radio convencional".

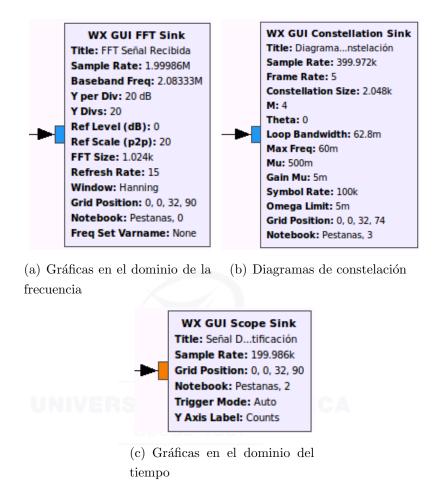

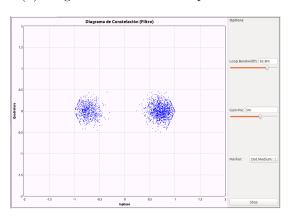

GNU Radio se instala en un computador personal, y para su funcionamiento, requiere de un componente de hardware externo capaz de recibir señales de RF, como es el receptor RTL-SDR 2832U. En este contexto, la evaluación de las técnicas de modulación se efectúa mediante *GNU Radio Companion GRC*, correspondiente a la interfaz de usuario gráfica de GNU Radio. Esta herramienta contiene

bloques predefinidos que permiten procesar, demodular señales y además almacenar datos, lo que posibilita la evaluación de sistemas de comunicación. Dentro de GRC se incluye la disponibilidad de bloques para observar el espectro de las señales recibidas, sus diagramas de constelación y diagramas en el dominio del tiempo.